# Electronics for Particle Measurement

# Hirokazu Ikeda ikeda@post.kek.jp School of Mathematical and Physical Science The Graduate University for Advanced Studies

June 6, 2002

#### Abstract

The basics of an integrated circuit are described with special emphasis placed on a charge-measurement system. Starting with an outline of a fine CMOS technology, the discussion moves to a practical implementation of circuits.

#### Contents

| <b>2</b> | 2 Basics about a MOSFET |                                   |    |  |  |  |  |

|----------|-------------------------|-----------------------------------|----|--|--|--|--|

|          | 2.1                     | Bibliography                      | ]  |  |  |  |  |

|          |                         | MOSFET                            |    |  |  |  |  |

|          | 2.3                     | Electronic properties of a MOSFET | 2  |  |  |  |  |

|          |                         | Example circuits with a MOSFET    |    |  |  |  |  |

|          | 2.5                     | SPICE parameters for a MOSFET     | 8  |  |  |  |  |

|          |                         |                                   |    |  |  |  |  |

| Α        | Get                     | ting started with SPICE           | 10 |  |  |  |  |

## 2 Basics about a MOSFET

#### 2.1 Bibliography

- P.R.Gray & R.G.Meyer, "Analysis and design of analog integrated circuits", John Wiley & Sons, 1984

- S.M.Sze, "Physics of semiconductor devices", John Wiley & Sons, 1981

#### 2.2 MOSFET

FET には、接合形 FET(JFET)、絶縁ゲート型(MOSFET 等) 、ショットキー接合FET(MESFET) などがある。

いずれも、ソース、ドレイン、ゲートの三端子からなる電子素子であって、ゲートに印加する電圧によって、ソースとドレイン間の伝導度を変調することにより、ソースとドレイン間に流れる電流を制御することができる点において共通する。

しかし、接合形 FET では、ゲートと伝導チャンネルがダイオード接合になっていて、ゲートに印加する電圧によってチャンネル断面の空乏層と伝導領域の割合を制御するようになっているのが特徴である。

FET stands for field effect transistor, which includes, junction FETs (JFET), insulated-gate transistors (MOSFET), and Schottky-barrier gate transistors (MESFET).

All of these electronic devices have three terminals called source, drain, and gate. The voltage applied to the gate relative to the source, i.e.  $V_{GS}$ , controls the conductivity between the drain and the source to modulate the carrier flow thereof.

As for the JFET, the interface between the gate and the conduction channel is maintained by a p-n junction. The depletion region develops from the gate toward the conduction channel to influence the cross section of the conduction channel.

一方、MOSFET では、ゲートと伝導チャンネルは、薄い酸化膜で絶縁されており、ゲートに印加する電圧によって、表面に形成された反転層の伝導度を制御するようになっているのが特徴である。

さらに、ショットキー接合形のFETでは、ゲートと伝導チャンネルは、金属・半導体のショットキー接合によって分離されており、ゲート電圧によって、絶縁基板とゲートに挟まれた伝導領域の空乏層と伝導領域の割合を制御するようになっているのが特徴である。

このように、それぞれ具体的な動作原理においては、相互に異なっている。一方、電子素子としてモデル化した場合には、共通する特徴が多いので、ここでは、最も一般的に用いられている MOSFET について、その詳細を議論することにする。なお、ショットキー接合形の FET は GaAs 系の化合物半導体に特有の技術であって、専ら、高周波領域での信号処理に用いられている。

On the other hand, the gate and the conduction channel of the MOSFET is separated by a thin film of silicon dioxide. The gate voltage induces a type-inversion on the surface of silicon to modulate the carrier flow between the source and the drain.

The gate-to-channel separation mechanism for the MESFET is a metal-to-silicon Schottky barrier. The operation mechanism is quite similar to that of the JFET.

In spite of the differences concerning the detailed operation principle, these three devices are characterized in a similar fashion as electronic devices. It appears to be sufficient to discuss only the MOSFET in detail. It is worth taking note that practical MESFETs are almost made of GaAs to be employed for a signal processing in a very high-frequency region.

### 2.3 Electronic properties of a MOSFET

バイポーラトランジスタには、npn トランジスタとpnp トランジスタとがあったように、MOSFET にも、n チャンネル・トランジスタ (pMOS) とp チャンネル・トランジスタ (pMOS) とがある。

n チャンネル・トランジスタは、伝導チャンネル部が p タイプであって、ゲートに伝導チャンネル相対で正の電圧を印加すると伝導チャンネルが n タイプに反転するようになっているトランジスタである。一方、p チャンネル・トランジスタは、伝導チャンネル部が n タイプであって、ゲートに伝導チャンネル相対で負の電圧を印加すると伝導チャンネルが p タイプに反転するようになっているトランジスタである。

以下、特に断らなければ、n チャンネル・トランジスタを前提として議論を進める。

バイポーラトランジスタにおいては、 $V_{BE}$  が指数 関数の肩にのっているため、ベース電圧の微小な変化によって、コレクタ電流を大幅に変えることができた。一方、MOSFET では、このような指数関数型の応答ではなく、高々 $V_{GS}$  の二乗に比例したドレイン電流応答が得られるにすぎない。

As in the case of the BJT, which consists of npn and pnp transistors, the MOSFET has two members, i.e. n-channel and p-channel MOSFET; they are called nMOS and pMOS, respectively.

The conduction channel of the nMOS transistor is made of p-type silicon whose surface is inverted into n-type by a positive voltage applied on the gate terminal. On the other hand, the conduction channel of the pMOS transistor is made of n-type silicon to be inverted into p-type by applying a negative voltage on the gate terminal.

We proceed the discussion while assuming that the designated transistors are n-MOS transistors, unless otherwise mentioned.

You might remember that the collector current is varied very quickly by a small voltage applied to the base terminal, which comes from the  $exp(qV_{BE}/kT)$  term appearing in the Ebers-Moll equation. On the other hand, the drain current of the MOSFET is proportional to no more than a quadratic term of  $V_{GS}$ .

しかし、MOSFET は、トランジスタの特性を、ゲートの形状 (W,L) によって大幅に制御できること、および、ゲートが絶縁されていること、ドレイン抵抗が高いこと、さらには、集積度を高くできること等の有利な特徴を有している。そこで、バイポーラトランジスタの適用領域においてもこれと競合すると同時に、さらに広範囲の適用領域を獲得してきている。

具体的には、MOSFET の直流特性は、ソース接地の形式で

The superiority of the MOSFET over the BJT, however, comes from several properties: that the characteristics of the MOSFET are widely adjustable by properly choosing the size of the transistor, i.e. (W,L); that the gate of the MOSFET is made of an insulator; that the output impedance of the drain node is in general much higher than that of the BJT; and that the minimum feature size of the MOSFET is much smaller than that of the BJT. In these respects, the MOSFET finds many application areas in state-of-the-art consumer electronics, even in those areas where the BJT has been predominantly employed.

In practice, the drain-current characteristics versus the gate voltage are described in a source-grounded configuration as follows:

$$I_{D} = \frac{k_{p}}{2} \frac{W}{L} \{ 2(V_{GS} - V_{TO})V_{DS} - V_{DS}^{2} \} (1 + \lambda V_{DS}) \text{ (where } V_{DS} \leq V_{GS} - V_{TO}),$$

$$I_{D} = \frac{k_{p}}{2} \frac{W}{L} (V_{GS} - V_{TO})^{2} (1 + \lambda V_{DS}) \text{ (where } V_{DS} > V_{GS} - V_{TO}).$$

のように表すことができる。第一式は、 $V_{DS} \leq V_{GS} - V_{TO}$  の領域での動作を表わすものであり、この領域を線形領域という。線形領域は、主にアナログスイッチとしての動作領域である

第二式は、 $V_{DS} > V_{GS} - V_{TO}$  の領域での動作を表わすものであり、この領域を飽和領域  $^a$ という。一般に、飽和領域は、増幅器を構成するときに用いられる動作領域である。

$^a$ バイポーラトランジスタでは、 $V_{CE} \ll V_{BE}$  となってコレクタ電流がほとんど流れなくなってしまっているような状況を指して飽和といっているので、両者を混同しない様に注意されたい。

ここで、 $k_p$  は、プロセスゲイン係数と呼ばれる量であり、ゲート酸化膜の単位面積当たりの容量  $C_{ox}$  と、ゲート直下の半導体表面でのモビリティーに比例する。

また、 $V_{TO}$  は、ゲート直下の半導体表面に導伝チャンネル(反転層)を形成するために必要なゲート電圧に対応する。

さらに、W と L は、ゲートの形状を表すためのパラメータであって、W は、ソースとドレーンが相対している横方向の距離をあらわし、L は、ソースとドレインを隔てている距離を表している $^a$ 。

$^o$ L の典型的な値は、毎年更新されている。 2 0 0 1 年現在では、 $0.6\sim0.3~\mu m$  となっている。また、酸化膜の厚みも同時に薄くなっている。 $L=0.6~\mu m$  プロセスに対応する、酸化膜厚みは、13~nm 程度である。

The first equation is for the linear region, which is defined as  $V_{DS} \leq V_{GS} - V_{TO}$ . A typical application in the linear region is for an analog switch.

The second equation is for the saturation region, which is defined as  $V_{DS} > V_{GS} - V_{TO}$ . Amplifiers are in general design so as to operate transistors in the saturation region. The term "saturation" is sometimes employed for a BJT in a totally different way; designating an operation condition where the collector current is almost cut off because of a lack of sufficient voltage across the collector and the emitter.

In the above equations,  $k_p$  is the process-gain factor, which is defined as the product of the unit capacitance between the gate and the conduction channel ( $C_{ox}$ ), and the mobility on the surface of the conduction channel ( $\mu_0$ ). These parameters are discussed again later.

$V_{TO}$  is virtually a gate voltage to induce a conduction channel (inversion layer) on the surface of silicon under the gate.

W and L designate the geometrical configuration of the gate. W is the length of the gate facing to the drain or the source. L is the distance between the drain and the source. A typical value for L is shortened every year. It was 0.6-0.3  $\mu m$  in the year 2001. The corresponding oxide thickness is about 13-7 nm.

$\lambda$  は、バイポーラトランジスタにおけるアーリー効果と類似の特性を表すために導入されたものであるが、物理的には、 $V_{DS}$  の増大により、実効ゲート長 (L) が短く見えるようになるためにドレイン電流が増大する現象を表現するためのパラメータである。

実際、上記第二式を $V_{DS}$ につき微分すると、

$\lambda$  is an artificial parameter to represent an effect which is similar to the Early effect appearing in the BJT. The drain current tends to increase for larger  $V_{DS}$  due to an effective shortening of L associated with the development of a depletion layer around the drain region.

In order to clarify the significance of  $\lambda$ , we try to differentiate the second equation with respect to  $V_{DS}$ , which yields

$$\frac{dV_{DS}}{dI_D} = \frac{1 + \lambda V_{DS}}{\lambda I_D}.$$

を得るから、ドレインにおける出力インピーダンス  $(r_o)$  は、 $\lambda$  に反比例していることが分かる。同時に、出力インピーダンスを高く設定するためには、ドレイン電流  $I_D$  を低減することが重要であることが分かる。

このことから、MOSFET は、酸化膜の厚み、ゲート形状等の幾何学的な形状によって、特性を大幅に調整できる可能性があることが分かる。ただし、 $V_{TO}$  については、これらの形状のみならず、チャンネル領域の不純物濃度にも依存する。その結果、 $V_{GS}=0$  でもドレイン電流を流すことができるようにすることもできる。このような FET をデプレッション型の FET という。一方、 $V_{GS}=0$  では、ドレイン電流が流れない FET をエンハーンスメント型の FET という。

ちなみに、 $\lambda=0$  のもとで第一式を  $V_{DS}$  で微分すると、

We understand, thereof, that the output impedance  $(r_o)$  at the drain node is inversely proportional to  $\lambda$ . As a by-product, we know that a reduction of the rain current is a key issue to achieve a higher output impedance.

Based on these equations, we understand that we could potentially set a wide range of the characteristics for the MOSFET by choosing such geometrical parameters as the oxide thickness and the gate configuration.  $V_{TO}$  is not necessarily a simple parameter, which depends on the impurity concentration in the channel region as well as the geometrical parameters mentioned above. As a result, we can have an FET which allows the drain current to flow even for  $V_{GS}=0$ ; these transistors are called "depletion FETs". On the other hand, the transistors which shut off any current for  $V_{GS}=0$  are called "enhancement FETs".

We try to go further to differentiate the first equation with respect to  $V_{DS}$  under the condition  $\lambda = 0$ , which yields:

$$\begin{array}{lcl} \frac{dI_D}{dV_{DS}} & = & k_p \frac{W}{L} (V_{GS} - V_{TO} - V_{DS}), \\ \\ R_{on}|_{V_{DS}=0} & = & \frac{1}{(V_{GS} - V_{TO}) k_p W/L}. \end{array}$$

となる。 $R_{on}|_{V_{DS}=0}$  を、 $ext{MOSFET}$  をアナログスイッチとして用いたときのオン抵抗 $^a$ という。

$^ak_p=20~\mu A/V^2~$ とし、 $V_{GS}-V_{TO}=4V,~W/L=10$ とすると、オン抵抗は  $1.25~k\Omega$  となる。

第二式を $V_{GS}$ で微分すると、

$R_{on}|_{V_{DS}=0}$  is called "on-resistance", when the transistor is employed for an analog switch.

The differentiation of the second equation with respect to  $V_{GS}$  yields

$$\frac{dI_D}{dV_{GS}} = k_p \frac{W}{L} (V_{GS} - V_{TO})(1 + \lambda V_{DS})$$

$$= \sqrt{2I_D k_p \frac{W}{L} (1 + \lambda V_{DS})}.$$

を得る。これを、トランスコンダクタンスといって、 $g_m$  の記号で表示する。これに対応するバイポーラ・トランジスタのトランスコンダクタンスは、 $\frac{1}{r_e} = \frac{I_E}{kT/q}$  であって、エミッタ電流に比例していたのであるが、MOSFET では、 $I_D$  のルートに依存するに過ぎないため、トランスコンダクタンスを大きくする目的で、ドレイン電流を増大させてもそれだけでは効率的でない。同時に W/L を増大させることも考慮する必要がある。

$\frac{dI_D}{dV_{GS}}$  is called "transconductance", which designates a transistor's ability to convert the gate voltage into the drain current. You should remember that the transconductance of the BJT is  $\frac{1}{r_e} = \frac{I_E}{kT/q}$ , which is proportional to the emitter current. The MOSFET is virtually inferior to the BJT, since the transconductance is proportional to the square root of  $I_D$ . In order to obtain a larger transconductance for a MOSFET circuit, we need to employ a larger W/L transistor as well as to allow a larger current for the transistor.

#### 2.4 Example circuits with a MOSFET

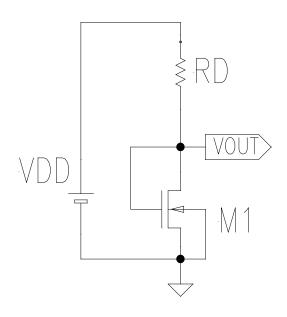

Figure 1: MOS diode.

図 1 には、ダイオード接続の MOSFET M1 において、ソースを接地し、ゲートとドレインを抵抗  $R_D$  を介して電源  $V_{DD}$  に接続した回路が示してある。

バイポーラトランジスタであれば、対応するコレクタの電位は、 $V_{BE}$  であるからほぼ一定の電圧として取り扱うことができるが、MOSFET では、そのような取扱いは、不適当である。

ドレイン電流と、抵抗  $R_D$  に流れる電流は、等しいから、飽和領域で動作していることを仮定すれば、ドレイン電圧を  $V_{out}$  として、

Fig.1 includes a MOSFET M1 whose gate and drain are connected together; M1 is configured as an nMOS diode. M1's source node is located at the ground potential, while the drain node leads to  $V_{DD}$  via  $R_D$ .

In order to figure out the DC voltage  $V_{OUT}$ , we need to solve the equation described below. If M1 were a BJT,  $V_{OUT}$  could be more or less 0.7 V.

Assuming that all of the drain current flows into the resistor  $R_D$ , we obtain

$$\frac{V_{DD} - V_{out}}{R_D} = \frac{k_p}{2} \frac{W}{L} (V_{out} - V_{TO})^2.$$

が成り立つ。上式は、 $V_{out}$  につき、二次方程式を与えるから、通常の方法によって解を得ることができる。

The above equation provides a quadratic equation with respect to  $V_{out}$ . The solution can be obtained as usual.

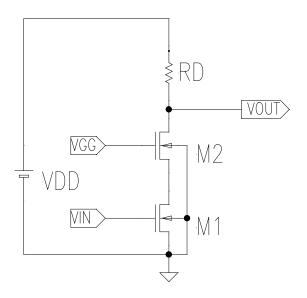

Figure 2: Cascode configuration.

図 2 は、MOS トランジスタ  $M_1$  と  $M_2$  とからなるカスコード回路である。M2 がいわゆるカスコードトランジスタであって、M1 は、通常のソース接地のトランジスタである。M1、M2 のトランスコンダクタンスとドレイン抵抗をそれぞれ、 $g_{m1}$ 、 $g_{m2}$ 、 $r_{o1}$ 、 $r_{o2}$  とおくと、M1、M2 のドレイン電流についての微少信号応答は、それぞれ以下の二式のように表わすことができる。

Fig.2 shows a so-called cascode circuit consisting of nMOS transistors, M1 and M2. The transistor M2 is a cascode transistor, while M1 is an ordinary source-grounded transistor. Assigning  $g_{m1}$ ,  $g_{m2}$ ,  $r_{o1}$ , and  $r_{o2}$  for the transconductances and the drain resistances of M1 and M2, respectively, we describe the small signal response of the drain currents for M1 and M2 as follows:

$$\begin{array}{rcl} i_{d1} & = & g_{m1}v_{g1} + \frac{v_{d1}}{r_{o1}}, \\ \\ i_{d2} & = & g_{m1}(-v_{d1}) + \frac{v_{d2} - v_{d1}}{r_{o2}}, \end{array}$$

ここで、 $i_{d1}=i_{d2}$  であることに注意されたい。そうすると、実効的な、トランスコンダクタンス  $(G_m)$  とドレイン抵抗  $(R_o)$  として、

where  $i_{d1} = i_{d2}$ . We then obtain the effective transconductance  $(G_m)$  and the drain resistance  $(R_o)$  as follows:

$$G_m = \frac{g_{m1}r_{o1}(g_{m2}r_{o2} + 1)}{r_{o1}r_{o2}g_{m2} + r_{o1} + v_{o2}},$$

$$R_o = r_{o1}r_{o2}g_{m2} + r_{o1} + r_{o2}.$$

$G_m$  は、 $g_{m1}$  とほぼ同程度の値を維持しながら、 $R_o$  については、格段にその値を高く設定することができるようになることが分かる。

$G_m$  does not move much from the original value of  $g_{m1}$ , while  $R_o$  can be much larger than either  $r_{o1}$  or  $r_{o2}$ .

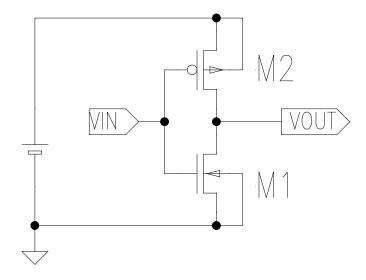

Figure 3: Inverter circuit.

図 3 は、pMOS と nMOS によるインバータ回路である。

回路図上pMOS は、ゲートに設けられた白丸によって、nMOS と区別することができる。しかし、むしろゲート端子に向き合っているチャンネ側 (バックゲート)に設けられた矢印の向きによって区別することが一般的である。矢印の向きは、反転現象によってバルクとチャンネル間に誘起されるダイオードの順方向に対応しているからである。回路構成は、交流的には、 $M_1$  と  $M_2$  の並列接続と考えることができるので、回路全体のトランスコンダクタンス・ゲインは、 $g_{m1}+g_{m2}$  であり、出力インピーダンスは、 $r_{o1}||r_{o2}$  である。

次に、直流特性を考える。 $M_1$  と  $M_2$  のそれぞれについて、

Fig.3 is an inverter circuit consisting of a pMOS (M2) and an nMOS (M1).

The pMOS transistor can be distinguished form the nMOS transistor by a small open circle attached at the gate terminal. An alternative way, but more common in practice, is to identify the nMOS or pMOS by the direction of the arrow attached at the backgate: the arrow for the nMOS directs to the gate, while the arrow for the pMOS directs outwards. The direction of the arrow designates the way from p to n of the diode induced by the surface inversion.

In a small signal analysis, M1 and M2 could be treated so configured as parallel. The effective transconductance of the entire circuit is  $g_{m1} + g_{m2}$ , and the effective output impedance is  $r_{o1} || r_{o2}$ .

We proceed to consider the DC characteristics. M1 and M2 obey the following quadratic equations:

$$I_{D1} = \frac{k_{p1}}{2} \frac{W_1}{L_1} (V_{in} - V_{TO1})^2,$$

$$I_{D2} = \frac{k_{p2}}{2} \frac{W_2}{L_2} (V_{DD} - V_{in} - |V_{TO2}|)^2.$$

が成り立つ。ここで  $V_{TO2}$  について絶対値をとっているのは、 ${

m pMOS}$  の  $V_{TO}$  は、負の値とするのがコンベンションだからである。

We note that  $V_{TO2}$  takes its absolute value in the second equation, which is due to the convention that the threshold voltage for the pMOS transistor is assigned to be negative.

$V_{in}$  と  $V_{out}$  とを開放とした上で、入力と出力をショーすると、 $I_{D1}=I_{D2}$  となって回路は平衡する。この時の電圧を  $V_{th}$  置くと、

Assuming that  $V_{in}$  and  $V_{out}$  are short-circuited without any other connections, the circuit moves to an equilibrium where  $I_{D1} = I_{D2}$ . The  $V_{in}$  or  $V_{out}$  under the equilibrium is designated as  $V_{th}$ , which is described as

$$V_{th} = \frac{\sqrt{k_{p1}W_1/L_1}V_{TO1} + \sqrt{k_{p2}W_2/L_2}(V_{DD} - |V_{TO2}|)}{\sqrt{k_{p1}W_1/L_1} + \sqrt{k_{p2}W_2/L_2}}.$$

を得る。

$V_{in} > V_{th}$  であれば、 $\operatorname{nMOS}$  のドレイン電流が支配的になって、出力の電圧は、低電位 (GND) レベルとなるが、逆に、 $V_{in} < V_{th}$  であれば、 $\operatorname{pMOS}$  のドレイン電流が支配的になって、出力の電圧は、高電位  $(V_{DD})$  のレベルに達する。

この性質を利用したのが、CMOS 方式の論理回路である。 $V_{th}$  は、W/L、 $k_p$ 、 $V_{TO}$  の選択により、かなり大幅に調整することが可能 $^a$ である。W/L は、回路設計段階での考慮対象であり、 $k_p$  と  $V_{TO}$  は、半導体プロセス条件における考慮の対象である。

$^a$ 例えば、 $M_1$  のドライブ能力を大きくすることによって  $V_{th}$  は低下する。具体的には、 $k_{p1}W_1/L_1=400~\mu A/V^2$ 、 $k_{p2}W_2/L_2=49~\mu A/V^2~V_{TO1}=|V_{TO2}|=1~V$  とすると、 $V_{th}=1.78~V$  となる。

ちなみに、 $k_{p1}W_1/L_1=k_{p2}W_2/L_2$ とすれば、 $V_{th}=V_{DD}/2$ とすることができるから、論理レベルの $\mathbf{H}$ と $\mathbf{L}$ の余裕が最大となる。これは、いわゆる  $\mathbf{TTL}$  論理回路との比較における一つの利点である。また、出力の論理レベルが確定した後は、 $M_1$ 、 $M_2$  のいずれにも電流が流れないので、低消費電力の論理回路を構成することができるという利点もある。

When  $V_{in} > V_{th}$ , the drain current of the nMOS transistor dominates over that of the pMOS transistor, and, hence,  $V_{out}$  moves to the ground potential. On the contrary, when  $V_{in} < V_{th}$ , the drain current of the pMOS transistor dominates to move the voltage of the output node toward  $V_{DD}$ .

These descriptions constitute the operation of a CMOS logic circuit, more specifically a CMOS inverter circuit.  $V_{th}$  could be widely adjusted by choosing appropriate W/L,  $k_p$ , and  $V_{TO}$ . If you adopt a larger W/L for M1,  $V_{th}$  is lowered. While W/L can be adjusted as a part of the circuit design,  $V_{TO}$  and  $k_p$  should be taken into account as the condition of the silicon process, if any.

If you set  $k_{p1}W_1/L_1 = k_{p2}W_2/L_2$ , it results that  $V_{th} = V_{DD}/2$ , and , hence,  $V_{th} - V_L$  and  $V_H - V_{th}$  are simultaneously maximized, where  $V_L$  and  $V_H$  are voltages corresponding to the logic low and logic high, respectively. This is one of the benefits of the CMOS circuit being quite different from that of TTL logic circuits. Another benefit concerns the power consumption. Once the output voltage is established, there is virtually no current flow across transistors M1 and M2, thus achieving low-power operation.

## 2.5 SPICE parameters for a MOSFET

SPICE パラメータとは、SPICE シミュレーション の用に供することを目的として調整され半導体素子を特徴づけるパラメータセットをいう。

集積回路の設計に着手するにあたっては、第一に抽象的な回路ブロックを VCVS や  $VCCS^a$ を用いて構成し、全体の回路動作を機能的側面から確認することが一般的である。

$^a \rm VCVS$ : Voltage-controlled voltage-source; VCCS: Voltage-controlled current-source

The SPICE parameter is a set of coefficients characterizing transistors employed for a SPICE simulation.

At the first step in circuit design, it is common to employ such function elements as VCVS and/or VCCS in place of transistors, which makes it easy to understand the behavior of an entire circuit.

しかし、実際の回路における増幅要素は、トランジスタの組み合わせとして構成されるべきものであるから、個々のトランジスタの特性が不明確であっては、本来あるべき回路の動作態様を確定することができない。

そこで、トランジスタを特徴づけるパラメータとして、各製造プロセスごとに PCM<sup>a</sup>等を用いて抽出された SPICE パラメータを用いるのが一般的である。

回路の基本要素を構築していくためには、ある程度基本的な SPICE パラメータを仮定する必要がある。

ここでは、 $0.6 - \mu m \ CMOS$  プロセスに一般的と考えられるパラメータを仮定して回路設計を提示するための基礎としようと思う。

そこで、表 1 に、回路設計の指針となるべき代表的な SPICE パラメータを示した。

On the other hand, the circuit design must eventually be completed as an assembly of transistors. We cannot make ourselves confident concerning the proper behavior of the circuit without knowing the exact characteristics of the transistors employed.

Every silicon foundry has a well-prepared PCM which can be employed for a SPICE parameter extraction.

In order to construct basic circuit blocks, we need to have working assumptions concerning the fundamental SPICE parameters.

In this lecture course, we are going to assume a  $0.6\mu m - CMOS$ , which is employed for designing example circuits.

Table 1 shows a very primitive SPICE parameter set of a 0.6  $\mu m-CMOS$ , which are still sufficient enough to guide a design principle.

| Symbol   | nMOS      | pMOS      |                                                      |

|----------|-----------|-----------|------------------------------------------------------|

| $t_{ox}$ | 1.3e-8    | 1.3e-8    | Oxide thickness $[m]$                                |

| $\mu_o$  | 544.      | 188.      | Surface mobility $[cm^2/Vs]$                         |

| $V_{TO}$ | 0.8       | -0.8      | Zero-bias threshold voltage                          |

| $N_{ch}$ | 1.7e + 17 | 1.7e + 17 | Peak impurity concentration near surface $[cm^{-3}]$ |

| dlc      | 4.e-8     | 4.e-8     | Offset length $[m]$                                  |

これらのパラメータから二次的に重要なパラメータ (表 2) を導くことができる。 すなわち、

These parameters are secondarily employed to derive important parameters (Table 2). They are:

$$C_{ox} = \frac{\epsilon_{ox}\epsilon_0}{t_{ox}},$$

$$k_p = C_{ox}\mu_o,$$

$$C_{GDO} = C_{GSO} = dlc * C_{ox}.$$

である。

$C_{ox}$  は、単位面積あたりのゲート容量を表わし、 $k_p$  は、プロセス利得係数を表わしている。なお、 $\epsilon_{ox}=3.9$  は、 $SiO_2$  の比誘電率、また、 $\epsilon_0=8.85~pF/m$  は、真空の誘電率である。さらにソースまたはドレイン部とチャンネル部の遷移部分とゲートとがオーバーラップすることにより  $C_{GDO}$  及び  $C_{GSO}$  が発生する。係数 dlc は、オーバーラップの幅を表わすパラメータである。

$C_{ox}$  is the unit gate capacitance;  $k_p$  is the process gain factor.  $\epsilon_{ox}$  is the dielectric constant of silicon dioxide.  $\epsilon_0$  is the permittivity in a vacuum. It is known that there exits a certain transient area from the source/drain area to the channel area. The overlap between the gate electrode and these transient areas, i.e. dlc, contributes to the so-called "overlap capacitance", i.e.  $C_{GDO}$  and  $C_{GSO}$ .

<sup>&</sup>lt;sup>a</sup>Process-control monitor

Table 2: Derived parameters.

| Symbol    | nMOS   | pMOS   |               |

|-----------|--------|--------|---------------|

| $C_{ox}$  | 2.7e-3 | 2.7e-3 | $[F/m^2]$     |

| $k_p$     | 145    | 50     | $[\mu A/V^2]$ |

| $C_{GDO}$ | 108    | 108    | [pF/m]        |

| $C_{GSO}$ | 108    | 108    | [pF/m]        |

因みに、最先端の MOSFET に適合する SPICE モデルは、100 以上のパラメータに依拠するものである。例えば、そのようなパラメータとして、サブスレッショールド領域の表現に優れる LEVEL=49(HSPICE)、LEVEL=7(PSPICE) を挙げることができる。

The SPICE parameters describing a state-of-the-art transistor consist of more than 100 items. The SPICE parameter LEVEL=49(HSPICE), or its equivalent LEVEL=7(PSPICE), is known to adequately describe the state-of-the-art MOSFET behavior, specifically in the sub-threshold region.

## A Getting started with SPICE

電子回路に親しむためには、実際に回路を構成して、その特性を評価することが最も実践的である。 しかし、有体物としての回路をいちいち構成する ことは、負担が大きすぎる。

そこで、SPICEシミュレータを用いて、回路の試作評価を仮想的に体験することが効率的であり、かつ、有効であると考える。

無償の SPICE シミュレータは、例えば、以下のサイトからダウンロードすることができる。

In order to be familiar with an electronic circuit, your practice of assembling and evaluating circuits is a mandatory part.

It loads too heavily to make up a circuit as a tangible object. A Spice simulator helps you to quickly learn circuit techniques by providing a virtual lab for wire soldering and electrical measurements.

A free-of-charge Spice simulator is available from the following internet site:

http://www.cadencepcb.com/products/downloads/PSpicestudent/default.asp

本講義においては、この SPICE シミュレータを適 宜使用しようと思うので、その起動方法等を紹介 して置こうと思う。

インストールが完了するとセットアップ実行ファイル Setup.exe を見つけることができる。これを起動すると Capture 及び PSpice の二つのフォルダーが作られる。PSpice にディレクトリーを移動すると PSPICE の実行ファイルである pspice.exe を見つけることができる。

pspice.exe を起動する前に mos.md、T001.sim.cir 等を各自の作業ディレクトリーに配置しておく。これらのファイルは、講義録の配信時に添付したものである。

pspice.exe を起動すると OrCAD PSpice A/D Demo と表示されたウィンドウが開く。そこで、バナーメニューを  $File \rightarrow open$  として T001.sim.cir をロードする。そうすると、T001.sim.cir (active) と表示されたサブウィンドウが開いて、そこに T001.sim.cir の内容が表示される。

In this lecture course, we are going to employ a Spice simulator when appropriate. A quick getting-started follows:

After completing the installation procedure, you will find an executable file, Setup.exe. The execution of Setup.exe generates two folders, Capture and PSpice. In the PSpice directory, you will find an executable code of PSpice, pspice.exe.

Prior to invoking pspice.exe, you locate those files as mos.md, and T001.sim.cir on your convenient work-directory. These files are attached in the E-mail together with the lecture notes.

Invoking pspice.exe, you will find a window named "OrCAS PSpice A/D Demo". In order to load the file T001.sim.cir, you follow the banner menu in such a way as  $File \rightarrow open$ . A subwindow named "T001.sim.cir(active)" appears on the window "OrCAS PSpice A/D Demo", where the contents of T002.sim.cir are shown.

Spice のエンジンを起動するためには、主ウインドウのバナーメニューを  $Simulation \rightarrow Run\ T001.sim$  とすればよい。

Spice の実行が完了すると、T001.sim.dat(active) と表示された解析結果を表示するためのサブウィンドウが開く。

最初の解析時には、このウィンドウには、グラフの枠が表示されているだけなので、バナーメニューを  $Trace \rightarrow Add\ Trace$  のように選択して、必要なノードを指定することにより所要の電圧波形等を得る事ができる。

以上

The Spice execution on T001.sim.cir is activated by following the banner menu in such a way as  $Simulation \rightarrow Run\ T001.sim$ .

Completion of the Spice execution is notified by the appearance of a sub window named T001.sim.dat(active), where the result of the Spice simulation is to be shown.

For the first time in your Spice simulation, there are shown no traces on the window, except for a plot-frame. Following the banner menu in such a way as  $Trace \rightarrow Add\ Trace$ , you can designate those nodes which you intend to examine their voltage wave forms and so forth.