# Electronics for Particle Measurement

## Hirokazu Ikeda ikeda@post.kek.jp School of Mathematical and Physical Science The Graduate University for Advanced Studies

June 14, 2002

#### Abstract

The basics of an integrated circuit are described with special emphasis placed on a charge-measurement system. Starting with an outline of a fine CMOS technology, the discussion moves to a practical implementation of circuits.

## Contents

| 3            |     | ic gates                          | 1  |

|--------------|-----|-----------------------------------|----|

|              | 3.1 | Inverter circuit                  | 2  |

|              | 3.2 | NAND2 circuit                     | 3  |

|              | 3.3 | NAND2 circuit with output inhibit | 4  |

|              | 3.4 | AND3 circuit                      | 4  |

|              | 3.5 | NOR2 circuit                      | 5  |

|              | 3.6 | Tri-state output buffer           | 6  |

|              | 3.7 | Selector                          | 7  |

|              | 3.8 | D-type flip-flop circuit          | 8  |

|              |     | 3.8.1 Gated inverter              | 8  |

|              |     | 3.8.2 Latch circuit               | 8  |

|              |     | 3.8.3 Master-slave configuration  | 9  |

|              |     | 3.8.4 EDFF circuit                | 10 |

|              | 3.9 | Example of a sequential circuit   |    |

|              |     | JTAG TAP controller               | 12 |

| $\mathbf{A}$ | Not | cice 1                            | ۱9 |

# 3 Logic gates

ロジックゲートとは、論理回路を構成するための 基本となる回路要素をいう。

アナログ集積回路においては、ロジック回路は、 無用であると考えるかも知れない。

しかし、コンパレータの出力信号の取り扱いや、 読み出し制御、及びテスト機能の一部として論理 回路を用いる事なしにシステムを構成することは 不可能である。 Logic gates constitute elementary building blocks to construct a logic circuit.

You might think that logic gates are useless for an analog circuit.

An analog circuit without any digital circuits is very rare in practice. Digital circuits are employed to handle comparator outputs, to control a readout sequence, and to implement a test pulse circuit. そこで、インバータ、NAND2 回路等の基本的なロジックゲートからはじめて、イネーブル端子付きのマスター・スレーブ D タイプ flip-flop(DFF) のようなより高度なロジック回路についても議論して置こうと思う。

なお、さらに高度な論理回路ブロックにつては、 これらの基本回路を組み合わせて、または、基本 回路から類推して構成していくことが可能である と考える。 We are going to describe digital circuits as a part of building blocks for an analog integrated circuit. Beginning with such basic gates as the inverter and the NAND2 circuit, we eventually reach more advanced circuit elements, where included are the D-type flip-flop and so forth.

Once you go through these digital circuits, you can proceed to configure more advanced circuits by yourself.

## 3.1 Inverter circuit

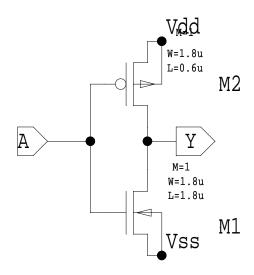

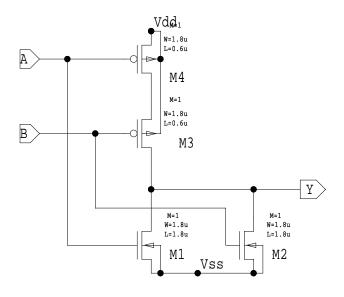

インバータ回路は、入力論理信号の H/L を反転した出力信号を生成するようになっている回路である。このような回路をインバータと呼ぶ。 図 1 にインバータ回路の具体例を示す。 The inverter circuit negates the logic level for the input terminal to deliver the inverted logic level at the output terminal.

Fig.1 shows a practical CMOS inverter circuit.

Figure 1: Inverter circuit.

インバータは、一個の pMOS トランジスタと、一個の nMOS トランジスタとから構成されている。これらのトランジスタのゲートは、共通の入力端子 A に接続されているため、A を介して供給される電圧信号が、"H"のときは、nMOS が導通して出力端子 Y には、"L"が出力され、一方、上記電圧信号が、"L"のときには、pMOS が導通して、出力端子 Y には、"H"が出力されるようになっている。

なお、W を  $1.8~\mu m$  と統一する一方、nMOS トランジスタの L を大きく採ることによって、pMOS と nMOS のドライブ能力の均等化を図っていることに注意して欲しい。

The CMOS inverter circuit consists of a pMOS FET (M2) and an nMOS FET (M1), whose gates are connected to a common input A, and whose drains are led to a common output Y.

When the input is in the "H" level, the nMOS is turned on to yield the "L" level at the output; when the input is in the "L" level, the pMOS is turned on to yield the "H" level at the output.

The W/L's for M1 and M2 are so designed as  $(W/L)_{M1}: (W/L)_{M2} = 1:3$ , which is to equalize the driving capability of these transistors. You should remember that the process gain factor for pMOS transistors is in general  $\approx 1/3$  of that for nMOS transistors. W/L's are so chosen to compensate for the  $k_p$  differences.

## 3.2 NAND2 circuit

NAND2 回路とは、論理信号を入力する二つの端子と、これら入力信号に対応する論理信号を出力する一つの端子とを有する論理素子であって、二つの入力端子に同時に"H"信号が加えられたときに、出力から"L"信号を送出し、一方、二つの入力信号うち少なくとも一方が"L"信号であるときには、出力から"H"信号を送出するようになっているものをいう。

図2に、NAND2回路の具体例を示す。

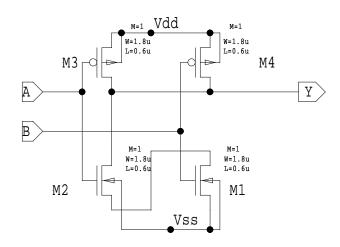

The NAND2 circuit has two input terminals, i.e. A and B, and one output terminal Y to deliver a logic level manipulated by the circuit.

When inputs A and B are simultaneously in the "H" level, the circuit delivers the "L" level at the output terminal. The logic level of the output Y is in the "H" level for the other combinations for A and B

Fig. 2 shows a practical CMOS NAND2 circuit.

Figure 2: NAND2 circuit.

NAND2 回路は、二個の pMOS トランジスタと、二個の nMOS トランジスタとから構成されている。 二つの pMOS トランジスタは、並列に配置されており、一方、二つの nMOS トランジスタは、直列に配置されているのが特徴的である。

なお、出力"L"のときのドライブ能力を確保するため、M1、M2 の L を  $0.6~\mu m$  としていることに注意して欲しい。

なお、同様の手法により、NAND3、NAND4、さらには、NAND5 のような回路を構成することができる。

The NAND2 circuit consists of two pMOS transistors (M3 and M4) and two nMOS transistors (M1 and M2). The pMOS transistors are located in parallel, while the nMOS transistors are located in series.

You may note that the L's for the nMOS transistors are set as 0.6  $\mu m$ , which is to maintain a certain driving capability at the "L" level.

In a similar fashion, you can construct those circuits, such as NAND3, NAND4, and even NAND5.

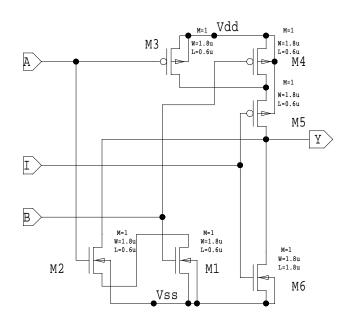

## 3.3 NAND2 circuit with output inhibit

NANDI 回路は、前項記載の NAND2 回路に出力インヒビット機能を付加したものである。すなわち、I端子の信号が'L"であれば、M5 は導通する一方、M6 は、ハイインピーダンスとなるから、回路は、M1 ないし M4 から構成される NAND2回路と同一の機能を果たす。ところが、I="H"では、M5 がハイインピーダンスとなり、M6 は、導通となるので、出力 Y は、A、B、入力の如何に関わらず強制的に"L"となるようになっている。

The NANDI circuit is not necessarily a generic logic gate. The NANDI circuit is similar to the NAND2 circuit, except for two additional transistors, M5 and M6; these additional transistors are employed to keep the output "L" at whatever are input levels for the inputs A and B.

In practice, as long as terminal I is "L", the NANDI circuit behaves exactly the same as the NAND2 circuit, since M5 is conducted while M6 is shut off. On the other hand, when terminal I is "H", the output terminal Y is forced to be "L", since M5 is shut off while M6 is conducted to  $V_{ss}$ .

Figure 3: NAND2 circuit with output inhibit.

## 3.4 AND3 circuit

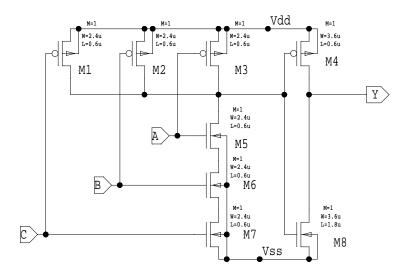

AND3 回路とは、A、B、C、三入力がいずれも"H" のときにのみ出力端子 Y に"H"を出力するようになっている回路要素をいう。

図 4 に AND3 回路の具体例を示した。

NAND2 回路を参考にすれば、その拡張として NAND3 回路を構成することができる。AND3 回 路は、かかる NAND3 回路の出力部にインバータ 回路を設けたものである。 The AND3 circuit delivers "H" only when inputs A, B, and C are simultaneously in the "H" level; otherwise, the output is kept at "L".

Fig. 4 shows a practical CMOS AND3 circuit.

You can construct a NAND3 circuit based on the NAND2 circuit. The AND3 circuit is accomplished by adding an inverter circuit on the output of the NAND3 circuit.

Figure 4: AND3 circuit.

## 3.5 NOR2 circuit

NOR2 回路とは、論理信号を入力する二つの端子と、これら入力信号に対応する論理信号を出力する一つの端子とを有する論理素子であって、二つの入力端子に同時に"L"信号が加えられたときに、出力から"H"信号を送出し、一方、二つの入力信号うち少なくとも一方が"H"信号であるときには、出力から"L"信号を送出するようになっているものをいう。

NOR2回路は、二個の pMOS トランジスタと、二個の nMOS トランジスタとから構成されている。二つの pMOS トランジスタは、直列に配置されており、一方、二つの nMOS トランジスタは、並列に配置されているのが特徴的である。

なお、同様の指針によって NOR3、NOR4、さらには、NOR5 等の回路を構成することができる。

The NOR2 circuit looks similar to the NAND2 circuit; the output Y for NOR2 is defined in a Boolean fashion as  $Y = \overline{A + B}$ , while that for the NAND2 circuit is  $Y = \overline{A \cdot B}$ .

The NOR2 circuit consists of two pMOS transistors (M3 and M4) and two nMOS transistors (M1 and M2), which is similar to the NAND2 circuit. The NOR2 circuit is distinguished from the NAND2 circuit by the series configuration for pMOS's and the parallel configuration for nMOS's.

In a similar fashion, you can presumably construct those logic gates, such as NOR3, NOR4, and even NOR5.

Figure 5: NOR2 circuit.

## 3.6 Tri-state output buffer

トライステートとは、出力の信号レベルとして"H/L"に加えて第三の状態としてハイインピーダンス状態を付加したものをいう。

ディジタル信号を取り扱う集積回路や、プリント 基板では、共通のデータ母線(以下、「データバス」 という。)を共用するように回路を構成すること が一般的である。

しかし、同時に複数のゲートが独立にデータバス を使用すると信号が衝突してしまいデータ伝送の 目的を果たす事ができない。

そこで、データバスを共用する出力ゲートは、"H/L"に加えてハイインピーダンス状態をとる事ができるようにして、出力ゲート同士が排他制御に服するようになっていることが必要である。トライステート・バッファーは、かかる目的を実現するための回路要素であって、浮遊容量を伴うデータバスを駆動するために電流容量が強化されているものである。

図6にトライステート・バッファーの回路例を示す。

The tri-stage buffer is so defined as a non-inverting buffer which is equipped with a capability to force its output in a high-impedance state. In an integrated circuit design as well as a printed-circuit design, it is quite common to employ a so-called "data-bus" which is shared by more than one circuit block for the purpose of the signal's I/O.

A possible contention between the activity of the involved circuit blocks should be resolved by a certain mechanism; otherwise, the signals on the databus will be mixed up.

It is required that the output gates which share the databus should be able to be in a high-impedance state in addition to the usual H/L states; the gates in the high impedance state do not bother the data transmission between any other gates.

The tri-state buffer is prepared to perform the above-mentioned capability with an intensified current-output capability to feed signals into a high-capacitve load.

Fig. 6 shows a practical CMOS tri-state buffer circuit.

Figure 6: Tri-state output buffer.

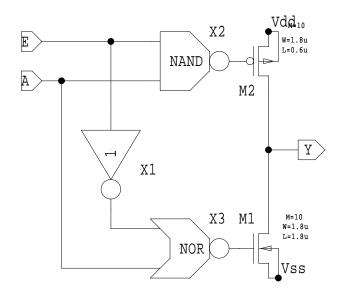

トライステート・バッファー回路は、インバータ回路 (X1) と、NAND 回路 (X2) と、NOR 回路 (X3) と、nMOS トランジスタ (M1) と、pMOS トランジスタ (M2) とから構成されている。

E 端子を介して供給される電圧信号が"H"のときは、X2、X3 は、A 端子を介して供給される電圧信号を反転してそれぞれの出力とし、M1、M2 を駆動する。したがって、Y 端子には、A 端子における電圧信号と同一の信号レベルを得ることができる。

一方、E 端子を介して供給される電圧信号が $^{\circ}$ L" のときは、A 端子に印加される電圧信号の如何にかかわらず、M2 のゲートは、 $^{\circ}$ H"に、M1 のゲートは、 $^{\circ}$ L"となるため、M1、M2 は、いずれも遮断される。したがって、Y 端子は、「ハイインピーダンス状態」となる。

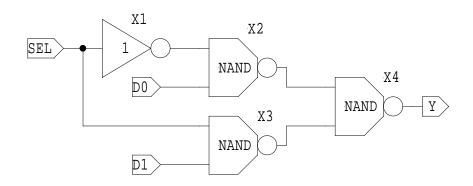

## 3.7 Selector

セレクターとは、二つの論理信号のうち、択一的 選択により、一方の論理信号を出力とするように なっている回路をいう。後述の順序回路において 具体的な使用方法が示されている。

図7には、具体的なセレクタ回路の構成例を示した。

X1 は、インバータ回路である。X2 ないし X4 は、NAND2 回路である。SEL 端子に印加された信号が"L"レベルのときには D0 信号が、"H"レベルのときには D1 信号が選択されて Y 端子にそれらと同一の論理レベルが出力されるようになっている。

The tri-state buffer consists of two transistors (M1 and M2), and three circuit blocks (X1, X2 and X3). X1 is an inverter circuit; X2 is a NAND2 circuit, and X3 is a NOR2 circuit.

When the signal level at the terminal E is "H", X2 and X3 just function as inverters to feed the inverted signal of the terminal A to the gate nodes of M2 and M1. The output level on the terminal Y is, therefore, the same as that on terminal A.

On the other hand, when the signal level at terminal E is "L", the gate node of M2 is kept "H", and the gate node of M1 is kept at "L", which simultaneously shuts off M1 and M2 to be in a high-impedance state.

The selector circuit selectively chooses either D0 or D1 to deliver the corresponding logic level at output terminal Y. A practical way to use the selector circuit is demonstrated in a later section concerning a sequential circuit.

Fig. 7 shows a practical CMOS selector circuit.

X1 is an inverter circuit. X2, X3 and X4 are NAND2 circuits. When SEL is "L", D0 is chosen; when SEL is "H", D1 is chosen.

Figure 7: Selector.

## 3.8 D-type flip-flop circuit

DFF とは、データ入力端子 (D) に加えられた信号レベルを、クロック端子 (CK) に加えられた信号レベルが"L"から"H"に遷移する瞬間にのみ出力端子 (Q) に取り込むようになっている回路要素である。本回路要素を理解するためには、以下のようなステップを経る必要がある。

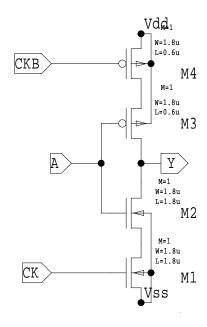

3.8.1 Gated inverter

DFF 回路は、いわゆるゲート付きのインバータ回路 (GINV) を応用して構成することができる。 GINV は、インバータ回路の  $V_{dd}$ 、及び  $V_{ss}$  との接続部にスイッチを設けて、スイッチがメイクしているときのみインバータとして働くようにしてあるものである。

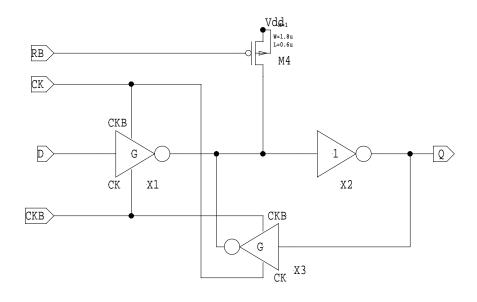

図8にGINVの構成例を示した。

M1、M4 は、それぞれ、CK 及びその反転信号である CKB 信号によって開閉されるスイッチである。 M1、M4 が導通しているときには、M2、M3 は通常のインバータとして動作するが、M1、M4 が非導通のときは、M2、M3 からなるインバータの出力は、M4 パイ・インピーダンス状態になっている。

## 3.8.2 Latch circuit

ラッチとは、入力に加えられた論理信号の"H/L" 状態を一時的に保持しておくようになっている回 路である。

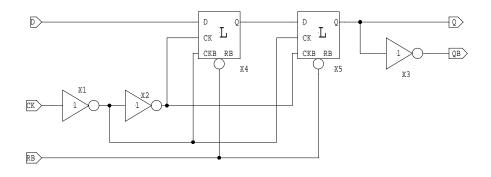

図 9 には、GINV を応用したラッチ回路 (Latch) の構成例を示した。

The DFF circuit acquires the logic level at terminal D at the transient from "L" to "H" of CK to deliver the output at the output terminal Q. In order to understand the exact nature of the DFF circuit, it requires some steps described below.

The DFF circuit includes a gated inverted circuit as a building block.

The gated inverter is basically an inverter circuit with additional switches in its  $V_{dd}$  and  $V_{ss}$  terminals.

Fig. 8 shows a practical CMOS gated inverter circuit.

The gated inverter circuit consists of two pMOS transistors (M3 and M4) and two nMOS (M1 and M2) transistors. M1 and M4 are introduced as switches driven by CK and CKB, respectively. When M1 and M4 are so driven as to be conducted, transistors M2 and M3 work as an ordinary inverter circuit. On the other hand, when M1 and M4 are shut off to isolate an inverter circuit made of M2 and M3, the output terminal Y is moved to a high impedance state.

The latch circuit temporarily stores a logic level fed into the input terminal.

Fig. 9 shows a practical CMOS latch circuit, where you will find gated-inverter circuits.

Figure 8: Gated inverter

ラッチ回路は、二個の  $\operatorname{GINV}(\operatorname{X1} \times \operatorname{X3})$  と、一個の  $\operatorname{INV1}(\operatorname{X2})$  と、一個の  $\operatorname{pMOS}$  トランジスタ  $(\operatorname{M4})$  とから構成されている。

D 端子の信号は、CK="L"のときに、信号レベルが反転されて X1 の出力にとりこまれ、さらに、もう一度反転されて、X2 の出力に達するようになっている。

引き続く CK="H"のタイミングにおいては、X1の出力は、ハイインピーダンスとなるとともに、X3は、X2の出力信号を反転して X2の入力に供給するようになっているので、X2、X3は、相互にその状態を保持するように助け合うようになる。このような状態を「ラッチが掛かった状態にある」という。

M4 のゲートには、RB 端子から電圧信号を印加できるようになっている。RB 端子の電圧を"L"とすると、X2 の入力部が  $V_{dd}$  に短絡されるので Q 端子の出力は、非同期に、かつ、X1 又は X3 の主張する出力レベルに係らず、強制的に"L"となるようになっている。M4 のドライブ能力のほうが、X1 又は X3 の出力トランジスタのドライブ能力に優っているからである。

#### 3.8.3 Master-slave configuration

DFF 回路は、ラッチ回路を二段従属接続することにより実現することができる。

図 10 に、DFF 回路の構成例を示した。

The latch circuit consists of two gated-inverter circuits (X1 and X3), one inverter circuit (X2), and a pMOS transistor (M4).

When CK is force to be "L", the logic level at the input terminal D is inverted by X1, and is once again inverted by X2 to be delivered at output terminal Q.

In the proceeding timing where CK is forced to be "H", the output of X1 moves to "Z", i.e. high impedance. On the other hand, X3 is activated to invert the signal level at the output terminal Q. X2 and X3 eventually help each other keep their states; the input signal is then "latched".

The transistor M4 is driven by RB. When RB is forced to be "L", the input node of X3 is conducted to  $V_{dd}$ , and, hence, the output terminal Q asynchronously moves to "L" irrelevant of the logic levels which X3 or X1 are otherwise to deliver. This behavior is guaranteed only when the driving capability of M4 overwhelms those of X1 or X3.

The D-type flip-flop includes two latch circuits employed in a cascaded fashion.

Fig. 10 shows a practical CMOS DFF circuit.

Figure 9: Latch circuit.

DFF 回路は、三個のインバータ (X1, X2, X3) と、二個のラッチ回路 (X4, X5) とから構成されている。ラッチ回路は、CK 信号と、その反転信号である CKB によって駆動される。X1, X2 は、これらの駆動信号を生成するようになっている。CK 信号が"L"の間に D 信号は、X4 の出力まで達するようになっているから、CK 信号が"H"に遷移すると同時に X4 の出力レベルが X5 の出力である Q 端子に現れる。X3 は、Q 端子の電圧を反転して QB 端子に供給するために設けられている。

このようにして、DFF は、その出力の遷移が必ず CK が  $L \rightarrow H$  と遷移する瞬間にのみ生ずることを保証している。

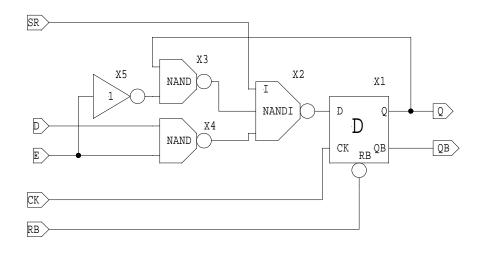

#### 3.8.4 EDFF circuit

一般に、同期回路の基本構成要素として頻繁に用いられるのが EDFF である。

EDFF とは、イネーブル端子付きの DFF の略称であって、イネーブル端子を介して印加される電圧信号が"H"レベルにあるときのみ、D 端子からの信号レベルが回路内部に取り込まれて Q 端子から出力されるようになっているものをいう。

図 10 にイネーブル端子付きの DFF の回路構成例を示す。

The DFF circuit consists of three inverter circuits (X1, X2 and X3) and two latch circuits (X4 and X5). The latch circuits are driven by CK and CKB, which are complementary to each other. X1 and X2 are employed to generate CK and CKB. While CK is "L", the signal applied on the input terminal D propagates to reach the output of X4. At the proceeding leading edge of CK, the output level of X4 is acquired by X5 to appear on the output terminal of X5, i.e. the terminal Q of the DFF circuit. X3 is provided to deliver the QB output.

In this way, it is guaranteed that the output logic state of the DFF circuit changes only at the leading edge of CK.

The EDFF circuit is a building-block frequently employed to design a synchronous circuit.

EDFF stands for a DFF circuit with an enable terminal. The EDFF circuit is activated only when terminal E is forced to be "H", acquiring the logic level applied for the input terminal D to deliver the output on terminal Q.

Fig. 10 shows a practical CMOS EDFF circuit.

Figure 10: D-type flip-flop circuit.

EDFF 回路は、DFF 回路 (X1) と、NANDI 回路 (X2) と、二個の NAND2 回路 (X3) X4) と、イン バータ回路 (X5) とから構成されている。NANDI 回路は、インヒビット端子を除けば NAND2 と同一の機能を有するから、X2 ないし X5 の回路は、全体としてセレクタ回路の機能を有していることがわかる。すなわち、E 信号が選択信号としての役割を果たしており、E="H"のときには、D 信号が選択されて X2 の出力となり、E="L"のとさるようになっている。したがって、E="L"である限り X1 の D 端子の信号レベルと Q 信号の信号レベルが同一に保たれる結果、X4 に加えられ D 端子の信号は、X1 に取り込まれる事はない。

X1の状態を維持するために CK 信号を阻止することも考えられる。しかし、阻止信号と CK 信号が非同期であるために、非常に幅の狭い信号が X1の CK 端子に印加されることも起こり得る。そうすると、ある場合には D 端子の信号が成功裡に取り込まれ、またある場合には、信号の取り込みに失敗するようなことになり得る。さらに、 CK 信号の幅の問題が発生しない場合においても、 X1の Q 出力の遷移するタイミングがクロック原振の Leading-edge と一致しない事から生ずる不具合の発生が考えられる。 EDFF は、このような不具合を解消したものであることに注意して欲しい。

The EDFF circuit consists of one DFF circuit (X1), one NANDI circuit (X2), two NAND2 circuits (X3 and X4), and one inverter circuit(X5). The circuit block consisting of X2 to X5 is identical to the selector circuit, except that X3 is a NANDI circuit instead of a NAND2 circuit. Terminal E is equivalent to the terminal SEL of the selector circuit. When E="H", the signal on terminal D is chosen to be acquired, and output Q is in accord with the level on terminal D. When E="L", the signal on terminal Q is chosen to be acquired, and the output at Q is kept as before. This means that the EDFF circuit is virtually inactive as long as terminal E is force to be "L".

You might think that the DFF circuit could be inactive by blocking the CK signal. You should be aware of the fact that the CK signal may be in general asynchronous to the possible blocking signal, irregularly yielding a narrow CK signal. Then, it may happen that the D input is successfully acquired at one time, and rejected at another time. Another problem concerns a disorder between the timing for the proper leading edge and the transition timing of the Q output. The EDFF circuit eliminates these possible issues.

Figure 11: D-type flip-flop with an "enable" input.

さらに、同様の問題は、いわゆるリセットについても発生し得る。EDFFには、二つのリセット端子がある。一つは、DFFに設けられているリセット端子 (RB) であって、これは、クロック信号とは非同期に DFF の Q 端子出力を"L"とすることができるものである。一方、SR 端子から加えられるリセット信号は、NANDIの出力を"L"とすることにより、クロック信号の Leading-edge で X1 の Q 出力を"L"とすることができるようになっている。 SR の名称は、同期型リセット (Synchronous reset) に因んだものである。一般的に、非同期リセットは、パワーオン・リセット時に専ら適用することとして、通常動作時には、同期リセットを用いることが望ましい。

# 3.9 Example of a sequential circuit JTAG TAP controller

TAP コントローラとは、"TMS"信号、"TCK"信号、及び"TRST"信号を受けて、JTAG の規定する順序回路を構成し、TDI 端子から TDO 端子に至る、シリアル信号の流れを指示するようになっている制御回路をいう。

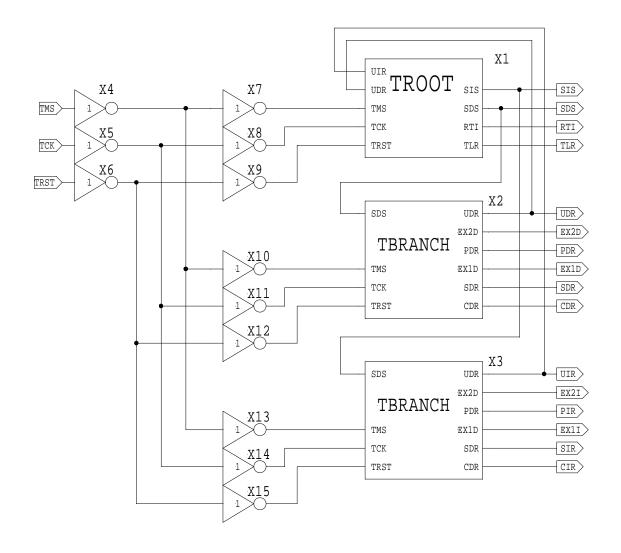

図 12 に TAP コントローラの構成例を示す。

A similar problem may happen to the reset timing. The EDFF circuit has two reset inputs: one is RB, which is equipped for the DFF circuit X1; the other is SR, which is equipped for the NANDI circuit X2. When terminal RB is force to be "L", the output Q of the DFF circuit asynchronously moves to "L" irrelevant of the CK timing. On the other hand, when terminal SR is forced to be "H", the output at Q of the DFF circuit moves to "L" at the leading edge of the CK signal. You should notice that SR stands for a synchronous reset. It is recommended to employ RB only for a purpose of a power-on reset, and to employ SR for general use.

The TAP controller is a sequential circuit defined as a part of the JTAG standard. The TAP controller circuit is driven by three JTAG-defined external signals ("TMS", "TCK", and "TRST") to control a bit-serial databus originating from a "TDI" terminal and reaching a "TDO" terminal. Fig. 12 shows an implementation of the TAP controller employing the above-mentioned logic gates.

Figure 12: Configuration of a TAP controller.

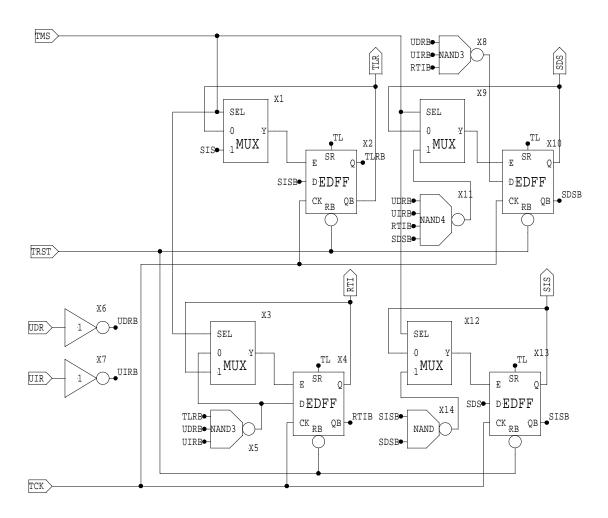

TAP コントローラは、X1(TROOT) の回路ブロックと、X2、及び X3(TBRANCH) の回路ブロックとから構成される。X1 の回路回路構成を図 13 に、X2、X3 の回路構成を図 14 に示す。

TROOT 回路は、4個のセレクタ回路 (X1、X3、X9、X12) と、4個の EDFF 回路 (X2、X4、X10、X13) と、2個のインバータ回路 (X6、X7) と、2個の NAND3 回路 (X5、X8) と、1個の NAND4回路 (X11) と、1個の NAND2 回路 (X14) とから構成されている。

The TAP controller circuits consists of one TROOT circuit (X1) and two TBRANCH circuits (X2 and X3). The internal configuration of the TROOT circuit is shown in Fig. 13. The internal configuration of the TBRANCH circuit is shown in Fig. 14.

The TROOT circuit consists of four selector circuits (X1, X3, X9, and X12), four EDFF circuits (X2, X4, X10, and X13), two inverter circuits (X6 and X7), two NAND3 circuits (X5 and X8), one NAND4 circuit (X11) and one NAND2 circuit(X14).

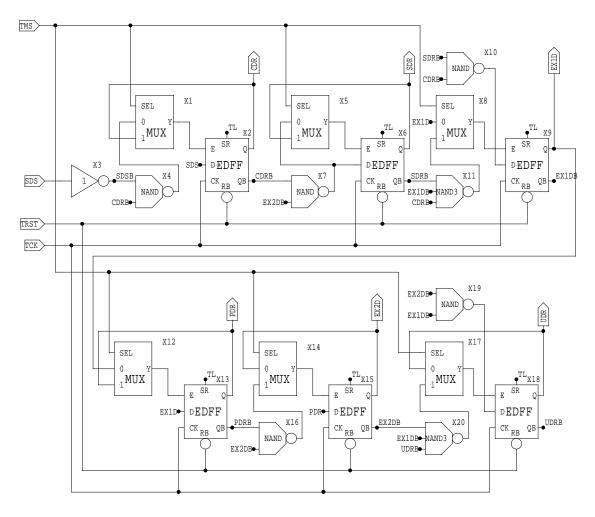

Figure 13: Schematic of TROOT.

TBRANCH 回路は、6個のセレクタ回路 (X1、 X5、X8、X12、X14、X17) と、6個のEDFF 回路 (X2、X6、X9、X13、X15、X18) と、1個のイン バータ回路 (X3) と、2個のNAND3 回路 (X11、 X20) と、5個のNAND2 回路 (X4、X7、X10、 X16、X19) とから構成されている。

TAP コントローラは、16の状態をとることができる。以下、それらの状態の意義と、遷移条件とについて概説する。

#### 1. Test-Logic-Reset:

The TBRANCH circuit consists of six selector circuits (X1, X5, X8, X12, X14 and X17), six EDFF circuits (X2, X6, X9, X13, X15 and X18), one inverter circuit (X3), two NAND3 circuits (X11 and X20), and five NAND2 circuits (X4, X7, X10, X16 and X19).

The TAP controller takes sixteen states; details of significance put for each state are described in the following together with conditions for the state transitions.

Figure 14: Schematic of TBRANCH.

回路上の信号名は、TLR である。この状態においては、すべてのテスト回路は、動作停止状態にあり、また、レジスタは、あらかじめ決められた初期値を保持するようになっている。一方、コア回路は、通常の動作をすることができるようになっている。次の状態へは、

$$\begin{split} TMS = 1: & \rightarrow & Run - Test/Idle, \\ TMS = 0: & \rightarrow & Test - Logic - Reset. \end{split}$$

のように遷移する。

2. Run-Test/Idle:

When TLR is "H", the TAP controller is in a state called "Test-Logic-Reset". Every circuit in the TAP controller is inactive and each register is set to a predetermined initial value. On the other hand, the core circuit operates as usual, since it is separated from the TAP controller. The conditions for a transition are as follows:

$$\begin{split} TMS = 1: & \rightarrow & Run - Test/Idle, \\ TMS = 0: & \rightarrow & Test - Logic - Reset. \end{split}$$

回路上の信号名は、RTI である。いわゆる、"built-in self test"機能が用意されているときには、この状態において実行される。当該機能が用意されていなければ、何らかのアクションが生じることはない。次の状態へは、

$$TMS = 1: \rightarrow Select - DR - Scan,$$

$TMS = 0: \rightarrow Run - Test/Idle.$

のように遷移する。

#### 3. Select-DR-Scan:

回路上の信号名は、SDS である。データレジスタを操作するためのブランチを選択するための補助的な状態である。次の状態へは、

$$TMS = 1: \rightarrow Select - IR - Scan,$$

$TMS = 0: \rightarrow Capture - DR.$

のように遷移する。

#### 4. Select-IR-Scan:

回路上の信号名は、SIS である。インストラクションレジスタを操作するためのブランチを選択するための補助的な状態である。次の状態へは、

$$TMS = 1: \rightarrow Test - Logic - Reset,$$

$TMS = 0: \rightarrow Capture - IR.$

のように遷移する。

#### 5. Capture-DR:

回路上の信号名は、CDRである。この状態において、シフトレジスタにデータをパラレルロードすることができる。パラレルロードは、TCKのrising-edgeにおいて実行する。次の状態へは、

$$TMS = 1: \rightarrow Exit1 - DR,$$

$TMS = 0: \rightarrow Shift - DR.$

のように遷移する。

## 6. Shift-DR:

回路上の信号名は、SDR である。シフトレジスタに蓄積されたデータは、TCK の rising-edge において TDI から TDO に向かって順送りされる(以下、「シフト過程」という)。次の状態へは、

$$TMS = 1: \rightarrow Exit1 - DR,$$

$TMS = 0: \rightarrow Shift - DR.$

のように遷移する。

When RTI is "H", the TAP controller is in a state called "Run-Test/Idle". If a built-in self-test capability is implemented, it can be executed in this state. No other action is allowed. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Select - DR - Scan,$$

$TMS = 0: \rightarrow Run - Test/Idle.$

When SDS is "H", the TAP controller is in a state called "Select-DR-Scan". This state is just an auxiliary state to branch to a series of states to manipulate data registers. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Select - IR - Scan,$$

$TMS = 0: \rightarrow Capture - DR.$

When SIS is "H", the TAP controller is in a state called "Select-IR-Scan". This state is just an auxiliary state to branch to a series of states to manipulate instruction registers. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Test - Logic - Reset,$$

$TMS = 0: \rightarrow Capture - IR.$

When CDR is "H", The TAP controller is in a state called "Capture-DR". In this state, each shift register acquires data from a PI terminal in such a way as a parallel load. The timing of the parallel load is the rising edge of TCK. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Exit1 - DR,$$

$TMS = 0: \rightarrow Shift - DR.$

When SDR is "H", the TAP controller is in a state called "Shift-DR". The data on the shift register is shifted toward downstream, i.e. a direction from TDI to TDO, at the rising edge of TCK; the procedure is called "shift process". The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Exit1 - DR,$$

$TMS = 0: \rightarrow Shift - DR.$

#### 7. Exit1-DR:

回路上の信号名は、EX1Dである。Capture-DR 状態において PI 端子から取り込んだデータを、 そのまま Update-DR 状態において PO 端子に 出力するために、Shift-DR 状態を経由せずに Update-DR 状態に至るブランチを提供してい る。次の状態へは、

$$TMS = 1: \rightarrow Update - DR,$$

$TMS = 0: \rightarrow Pause - DR.$

のように遷移する。

#### 8. Pause-DR:

回路上の信号名は、PDR である。本状態は、一時的にシフトレジスタのシフト過程を停止させたい場合に用いられる。次の状態へは、

$$TMS = 1: \rightarrow Exit2 - DR,$$

$TMS = 0: \rightarrow Pause - DR.$

のように遷移する。

## 9. Exit2-DR:

回路上の信号名は、EX2D である。Pause-DR 状態から Update-DR 状態、又は SHIFT-DR 状 態へ遷移するためのブランチを提供している。 次の状態へは、

$$TMS = 1: \rightarrow Update - DR,$$

$TMS = 0: \rightarrow Shift - DR.$

のように遷移する。

## 10. Update-DR:

回路上の信号名は、UDRである。この状態に入ると、シフト過程が完了する。そこで、テストデータレジスタの内容を、TCKの falling edgeで更新することができる。次の状態へは、

$$TMS = 1: \rightarrow Select - DR - Scan,$$

$TMS = 0: \rightarrow Run - Test/Idle.$

のように遷移する。

#### 11. Capture-IR:

When EX1D is "H", the TAP controller is in a state called "Exit1-DR". This state provides an option to skip Shift-DR state to reach Update-DR state where each shift register delivers its data-bit to a PO terminal. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Exit1 - DR,$$

$TMS = 0: \rightarrow Shift - DR.$

When PDR is "H", the TAP controller is in a state called "Pause-DR". This state is employed to temporarily pause the shift process. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Exit2 - DR,$$

$TMS = 0: \rightarrow Pause - DR.$

When EX2D is "H", the TAP controller is in a state called "Exit2-DR". This state provides a transit from Pause-DR to either Update-DR or Shift-DR The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Update - DR,$$

$TMS = 0: \rightarrow Shift - DR.$

When UDR is "H", the TAP controller is in a state called "Update-DR". Arriving at this state, the shift process is completed to be allowed to update a test-data-register at the falling edge of TCK. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Select - DR - Scan,$$

$TMS = 0: \rightarrow Run - Test/Idle.$

回路上の信号名は、CIR である。この状態において、あらかじめ設定されているインストラクションレジスタの内容をシフトレジスタにパラレルロードすることができる。パラレルロードは、TCK の rising-edge で実行される。次の状態へは、

$$TMS = 1: \rightarrow Exit1 - IR,$$

$TMS = 0: \rightarrow Shift - IR.$

のように遷移する。

#### 12. Shift-IR:

回路上の信号名は、SIR である。Shift-DR と同様の意義を有する。次の状態へは、

$$TMS = 1: \rightarrow Exit1 - IR,$$

$TMS = 0: \rightarrow Shift - IR.$

のように遷移する。

#### 13. Exit1-IR:

回路上の信号名は、EX1Iである。Exit1-DR と同様の意義を有する。次の状態へは、

$$TMS = 1: \rightarrow Update - IR,$$

$TMS = 0: \rightarrow Pause - IR.$

のように遷移する。

## 14. Pause-IR:

回路上の信号名は、PIR である。Pause-DR と同様の意義を有する。次の状態へは、

$$TMS = 1: \rightarrow Exit2 - IR,$$

$TMS = 0: \rightarrow Pause - IR.$

のように遷移する。

#### 15. Exit2-IR:

回路上の信号名は、EX2Iである。Exit2-DR と 同様の意義を有する。次の状態へは、

$$TMS = 1: \rightarrow Update - IR,$$

$TMS = 0: \rightarrow Shift - IR.$

のように遷移する。

#### 16. Update-IR:

When CIR is "H", the TAP controller is in a state called "Capture-IR". In this sate, each shift register acquires the content of the instruction register in such a way as a parallel load at the rising-edge of TCK. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Exit1 - IR,$$

$TMS = 0: \rightarrow Shift - IR.$

When SIR is "H", the TAP controller is in a state called "Shift-IR", which is similar to the state Shift-DR. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Exit1 - IR,$$

$TMS = 0: \rightarrow Shift - IR.$

When EX1I is "H", the TAP controller is in a state called "Exit1-IR", which is similar to the state Exit1-DR. The conditions for a transition are as follows

$$TMS = 1: \rightarrow Update - IR,$$

$TMS = 0: \rightarrow Pause - IR.$

When PIR is "H", the TAP controller is in a state called "Pause-IR", which is similar to the state Pause-DR. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Exit2 - IR,$$

$TMS = 0: \rightarrow Pause - IR.$

When EX2I is "H", the TAP controller is in a state called "Exit2-IR", which is similar to the state Exit2-DR. The conditions for a transition are as follows:

$$TMS = 1: \rightarrow Update - IR,$$

$TMS = 0: \rightarrow Shift - IR.$

回路上の信号名は、UIR である。この状態において、シフトレジスタの内容をインストラクションレジスタに設定することができる。設定は、TCK の falling-edge において実行される。次の状態へは、

$TMS = 1: \rightarrow Select - DR - Scan,$  $TMS = 0: \rightarrow Run - Test/Idle.$

のように遷移する。

When UIR is "H", the TAP controller is in a state called Update-IR. In this state, each bit of the instruction register is updated by the output of the shift register at the falling edge of TCK. The conditions for a transition are as follows:

$$\begin{split} TMS = 1: & \rightarrow & Select - DR - Scan, \\ TMS = 0: & \rightarrow & Run - Test/Idle. \end{split}$$

## A Notice

レポート課題 (2)

世界中の有力な半導体メーカーは、微細化技術を 競っていますが、微細化するとどのような利益が あるのでしょうか?

Subject for report (2)

Major semiconductor industries in the world are competing with each other to make a finer integrated circuit. What is the benefit of a fineprofile integrated circuit?

以上