# アナログVLSIの開発と フロントエンドIP

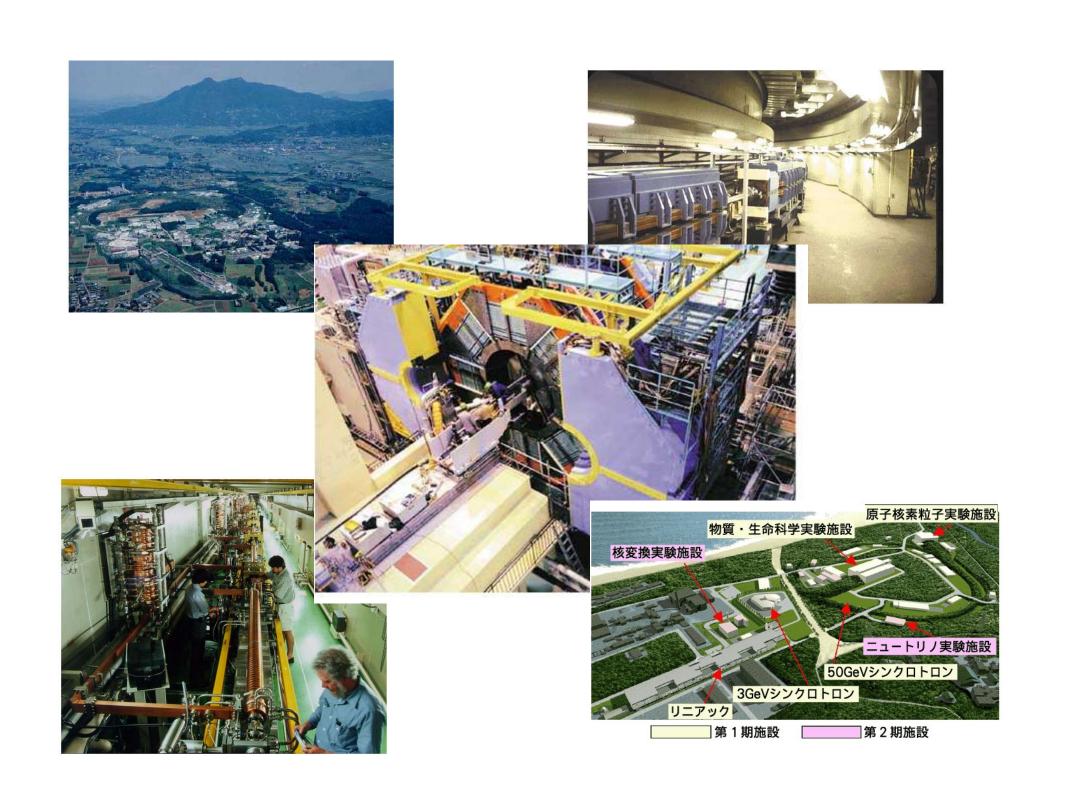

高エネルギー加速器研究構・素粒子原子核研究所 (宇宙科学研究所・次世代探査機研究センター・ 宇宙センサー併任)

池田 博一

# BELLE SECTION SECTION

#### 高エネルギー物理

# 集積回路化の要請

結果的に両分野の要請は近接してきている。

宇宙科学

素粒子識別能力向上を 目的とする検出器の セグメント化 ■

信号ケーブルの削減 と信号品質の確保 小型・軽量・低消費電力 の要請等が新たに発生

小型·軽量·低消費電力 機械的な信頼性 部品点数の削減の潜在的要請 +

検出器の複眼化(画像的な観 測)

# アブストラクト

近年サブミクロンCMOSプロセスを利用したセンサー用アナログVLSIの開発が大学や研究所で行われるようになってきた。本講演では、開発上の技法について回路設計からシミュレーション、レイアウトにいたる過程を具体的に解説する。あわせて、今後の動向や、CMOSアナログ回路設計の標準化(フロントエンドIPの開発状況)の試みを紹介する。

「Electronics」第一章を参照して下さい。

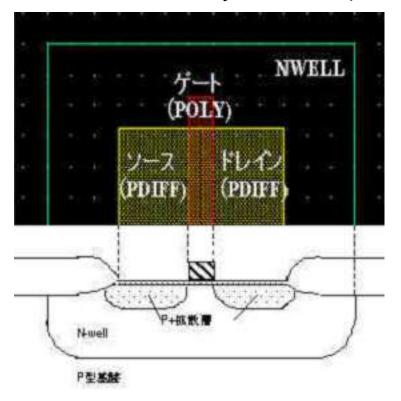

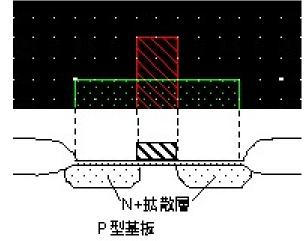

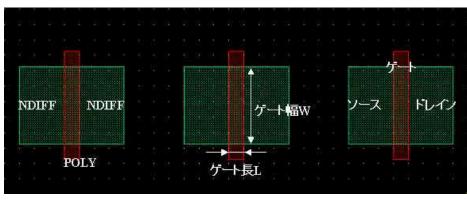

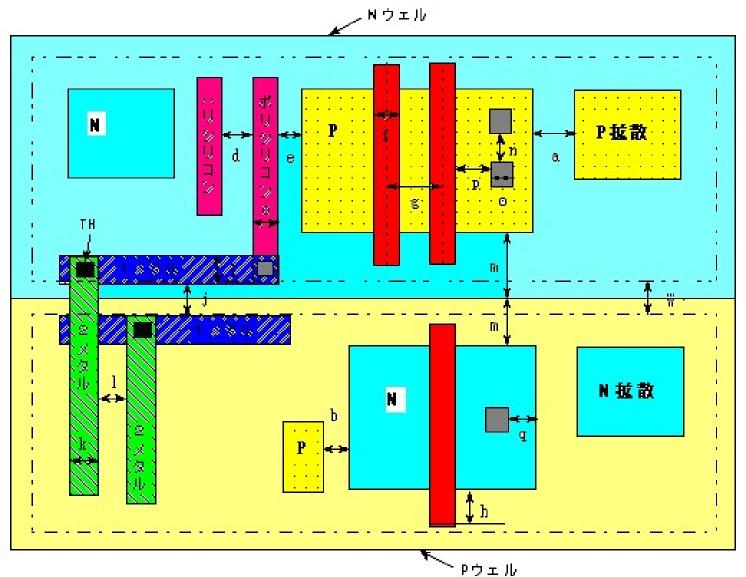

# CMOSプロセスとは

シリコンをベースとする半導体製造技術であって、相補型絶縁ゲート型 FET を備えたものをいう。

#### PMOSトランジスタ

#### NMOSトランジスタ

# CMOSプロセスの特徴

#### 一般的な特徴

- 1) 高集積・低電力回路に適合

- 2)アナログとディジタルの混成による複雑な回路構成が可能

- 3)製造技術の成熟度が高い

- 4) 静電気に弱い

- 5) 高抵抗素子·大容量不可

- 6)電源耐圧が低い

- 7)素子の絶対値は、あてにできないが、相対精度は良好である

- 8)放射線耐性については、SOI-CMOSの利用により克服できる

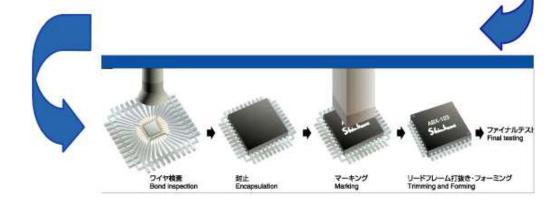

#### 0.35umCMOSの諸元

ゲート酸化膜: 7.2 nm

ゲート最小幅: 0.4 um

メタル最小幅: 0.6 um

メタル最少間隔:1 um

高抵抗:2.35 kOhm/sq

容量:1.8 fF/um\*\*2

動作保証電圧:2.7-3.6 V

# 集積回路設計の流れ

仕様策定

機能記述

回路記述+検証

レイアウト設計+検証

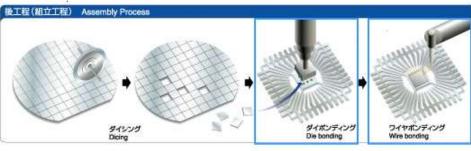

シリコンプロセス(前工程+後工

程)

回路の入手

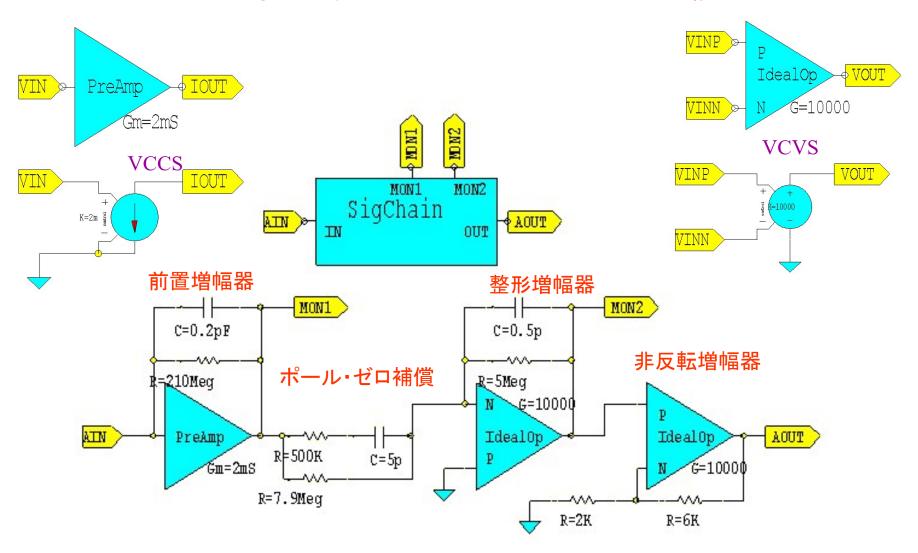

# 信号チェインの抽象的記述

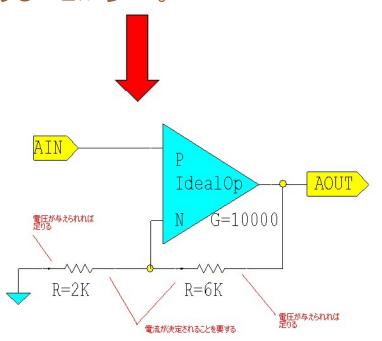

VCCS、VCVS、抵抗、容量等を用いて理想的な回路を構成すること

### SPICE NETLISTの生成

#### 回路図をSPICE仕様のネットリストに変換する

\* SPICE netlist written by S-Edit Win32 7.03

.SUBCKT IdealOp VINN VINP VOUT Gnd

e1 VOUT Gnd VINP VINN 10000

.ENDS

.SUBCKT PreAmp IOUT VIN Gnd

gl IOUT Gnd VIN Gnd 2m

.ENDS

.SUBCKT SigChain AIN AOUT MON1 MON2 Gnd

X1 MON1 AIN Gnd PreAmp

X2 N3 Gnd MON2 Gnd IdealOp

X3 N1 MON2 AOUT Gnd IdealOp

C1 AIN MON1 0.2pF

C2 N2 N3 5p

C3 N3 MON2 0.5p

R4 AIN MON1 210Meg TC=0.0, 0.0

R5 N3 MON2 5Meg TC=0.0, 0.0

R6 N1 AOUT 6K TC=0.0, 0.0

R7 Gnd N1 2K TC=0.0, 0.0

RP MON1 N2 500K TC=0.0, 0.0

RZ MON1 N3 7.9Meg TC=0.0, 0.0

.ENDS

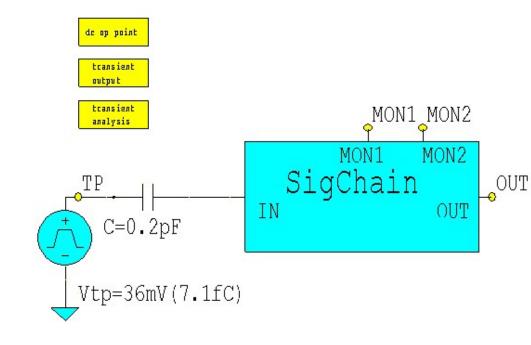

\* Main circuit: T000

X1 N1 OUT MON1 MON2 Gnd SigChain

C1 TP N1 0.2pF

.op

v2 TP Gnd pulse(0.0 36m 100n 10n 10n 100u 200u)

.tran  $10n\ 50u$

.print tran v(VTP) v(MON1) v(MON2) v(OUT)

\* End of main circuit: T000

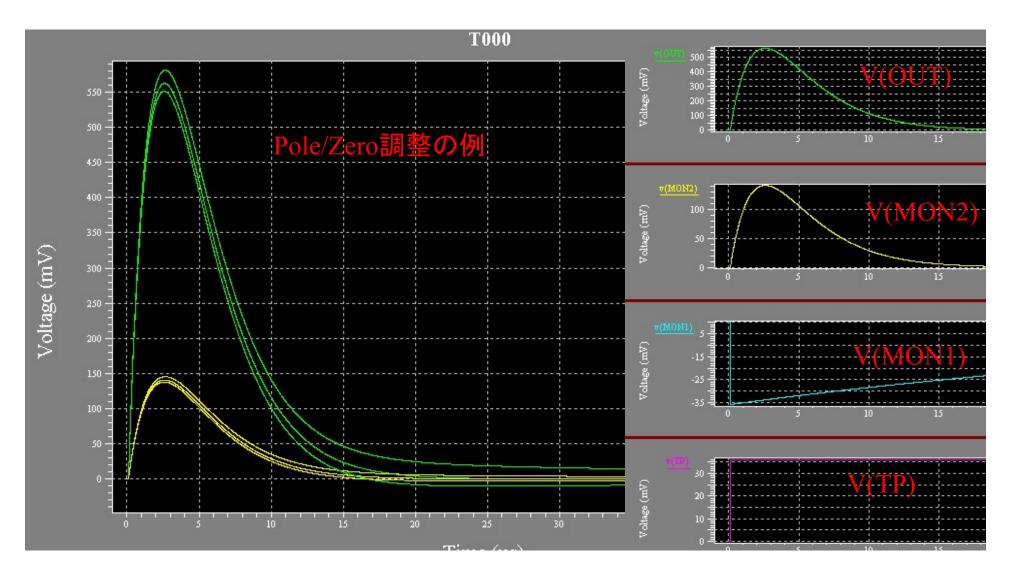

# SPICEの実行

仕様の具体化:素子値の決定、信号スケールの確認等

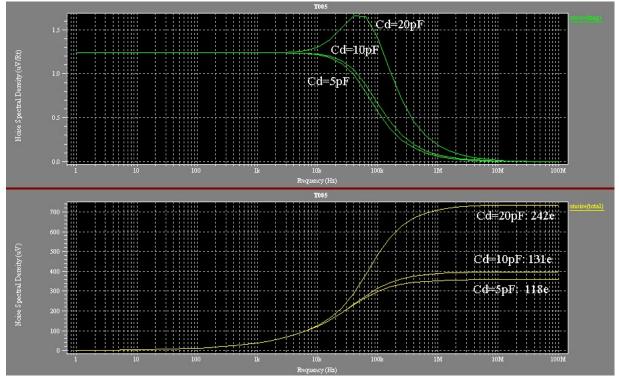

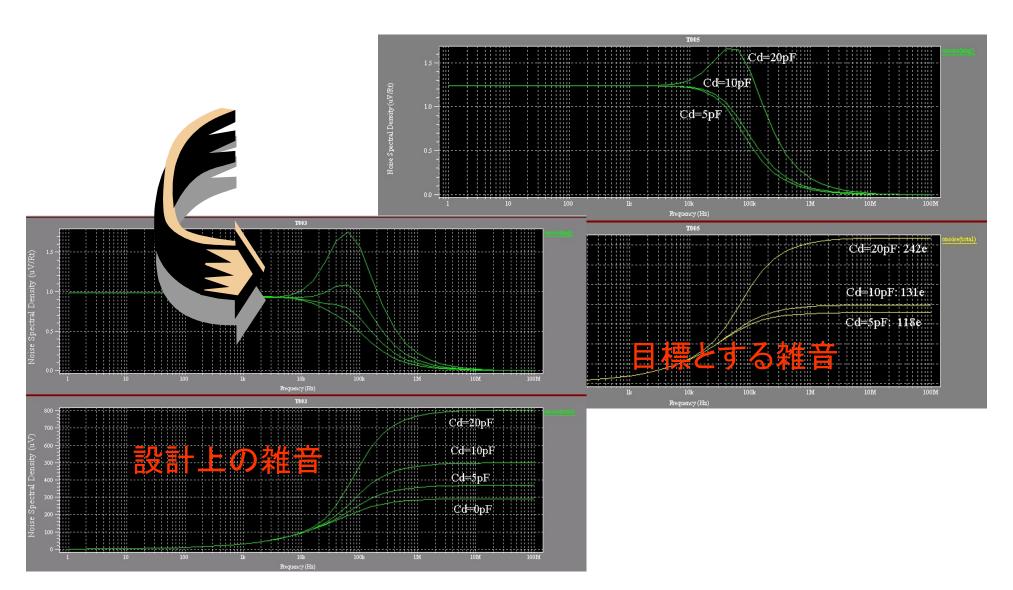

# 電子雑音の見積

電子雑音とは、検出器で生成される電荷に換算された雑音をいう

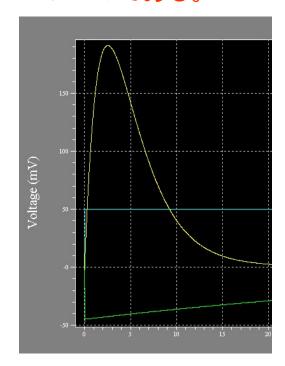

10fC(50mV\*0.2pF) の入力電荷に対し て出力電圧は、 191mVである。

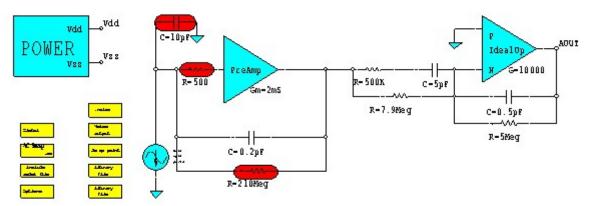

## 回路設計

#### 仕様上要求される性能を実現することを目的として所要の 機能をMOSFETを用いて実現すること

回路ブロックの設計と確認(DC解析、AC解析、パルス応答)

高抵抗、大容量は使えない!

信号チェインの組上げと確認

確認対象以外は抽象記述で!

チップの組上げと確認

収束条件を整えるために悪戦苦闘!

SKEWパラメータによる確認(FAST、TYPICAL、SLOW)

特性ばらつきに対する対応策!

# 抵抗回路

一方の端子から見ると抵抗と同様にふるまうが、他方の端子からみると 無限大の抵抗を有する素子をいう。

一般に電子回路では、抵抗の 端子間に発生する電流は、一 方の端子においてのみ有用で あり、他方の端子には不要で あることが多い。

MOSトランジスタを用いて100メガオー ムクラスの抵抗を構成することができる

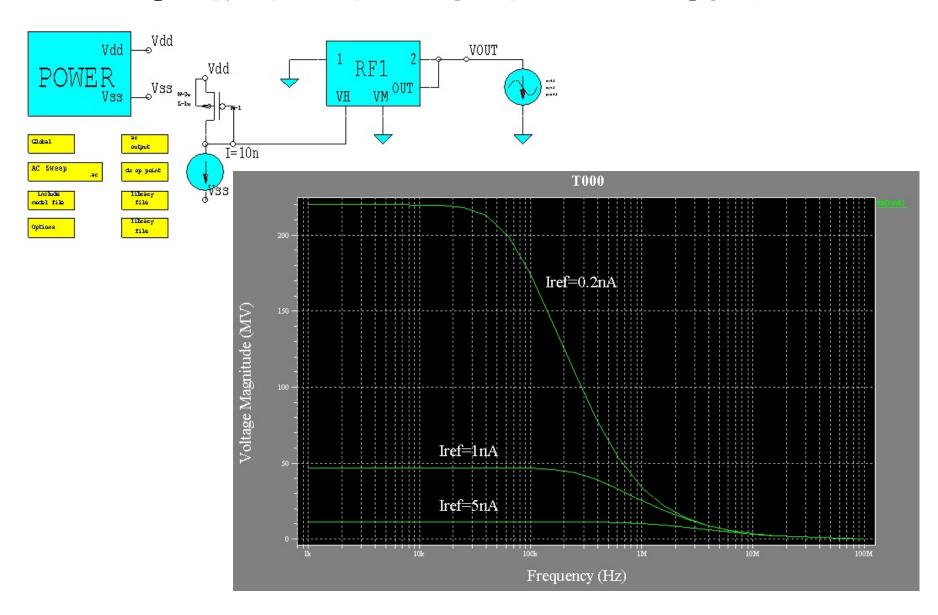

# 抵抗回路の特性(AC解析)

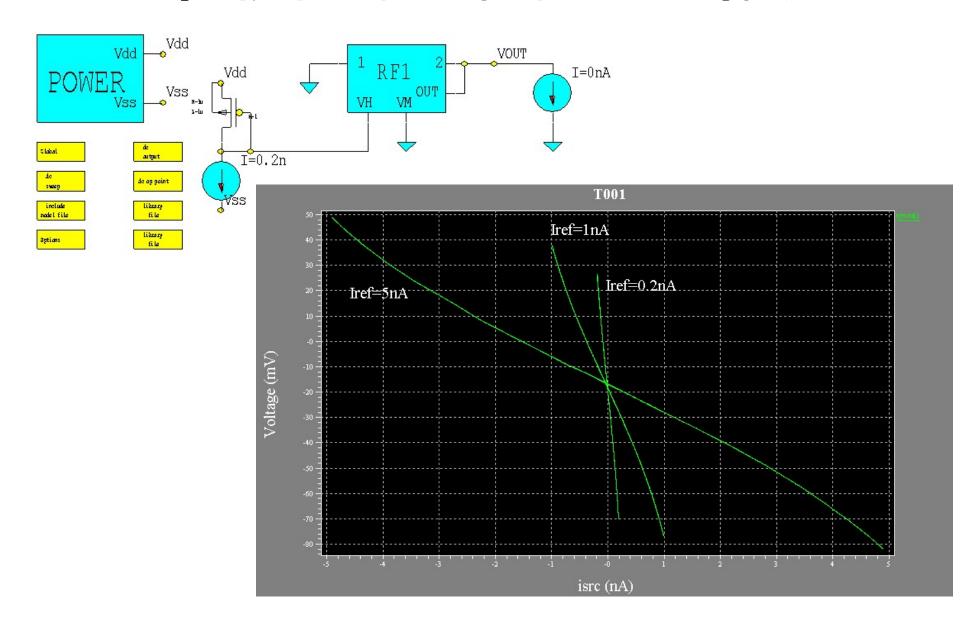

# 抵抗回路の特性(DC解析)

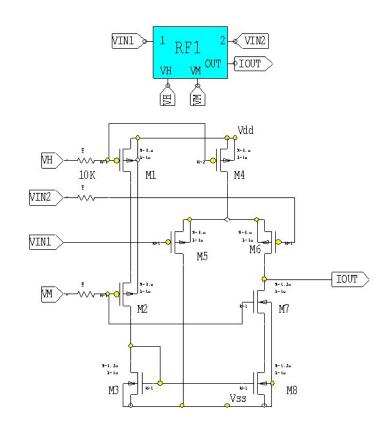

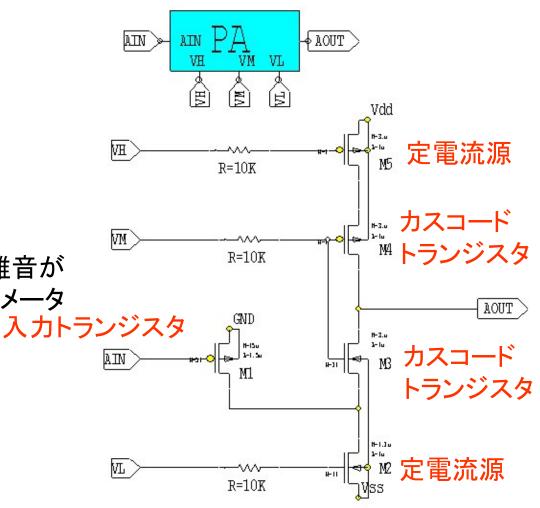

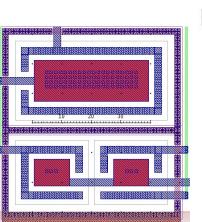

# 前置增幅器

検出器の発生する電荷信号を積分して電圧信号に変換する増幅器 であって、特に低雑音特性を有するものをいう

入力トランジスタとして W=15um L=0.5um M=50の PMOSトランジスタを用いた Folded-cascode型の増幅器 である。

- 1)大きなトランジスタで雑音の 発生を抑制

- 2)PMOSは、NMOSよりも1/f雑音が 少なめ、かつ放射線よるパラメータ 変動も少ない 入力ト

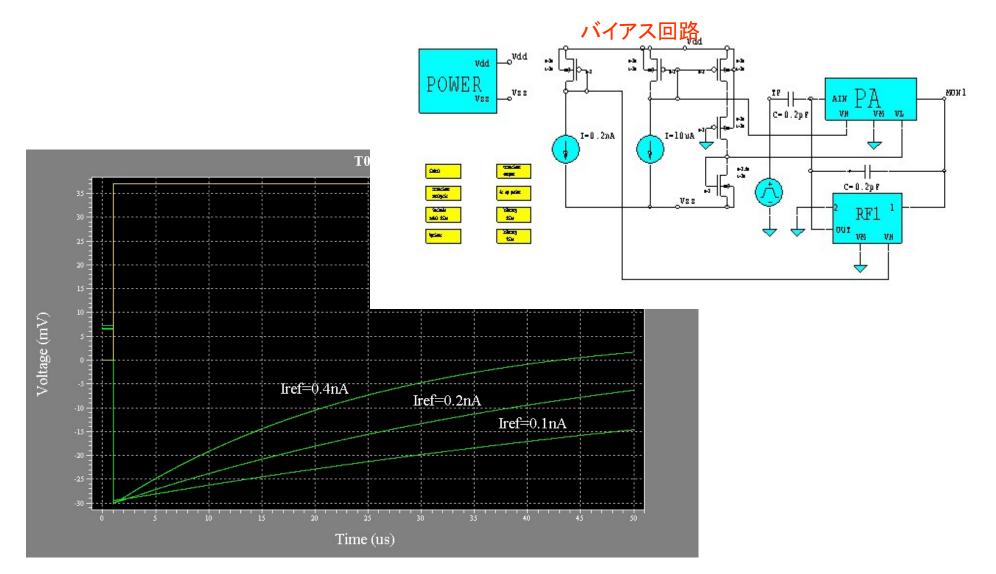

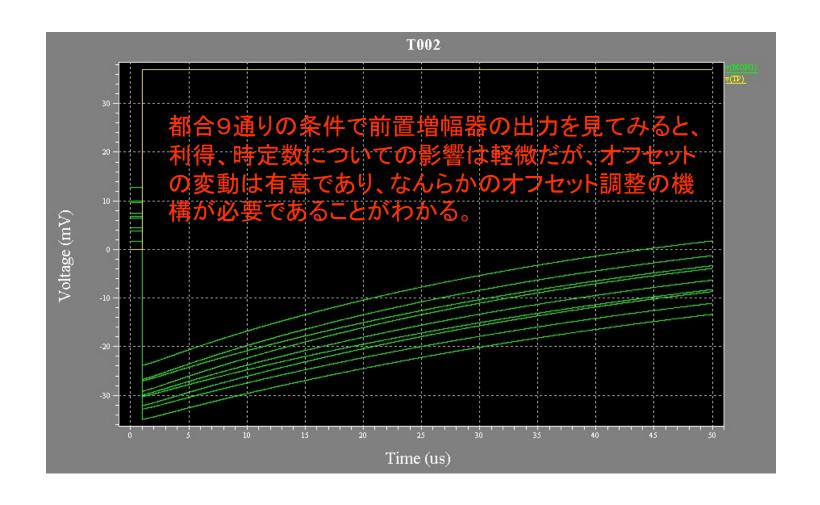

# パルス応答の確認

抵抗回路及び帰還容量を付加して荷電増幅器として機能させる

# 電子雑音の確認

実回路では、さまざまな雑音源が関与する。

# ® SKEWシミュレーション

半導体プロセスのずれ込みの限界(F,T,S)における回路動作の確認である。併せて温度に対する感度、さらには、放射線損傷モデルが入手可能であれば、是非動作確認をしておきたいところである。

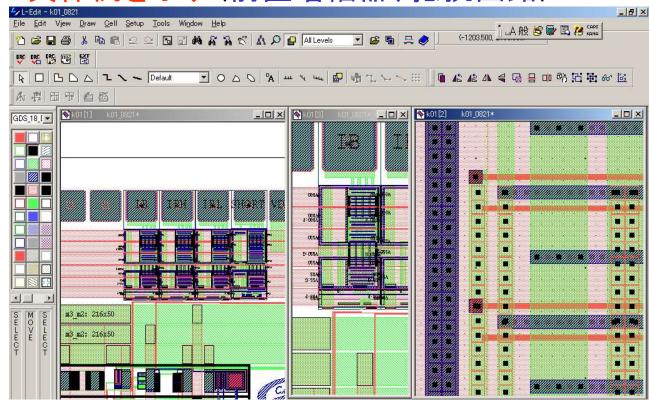

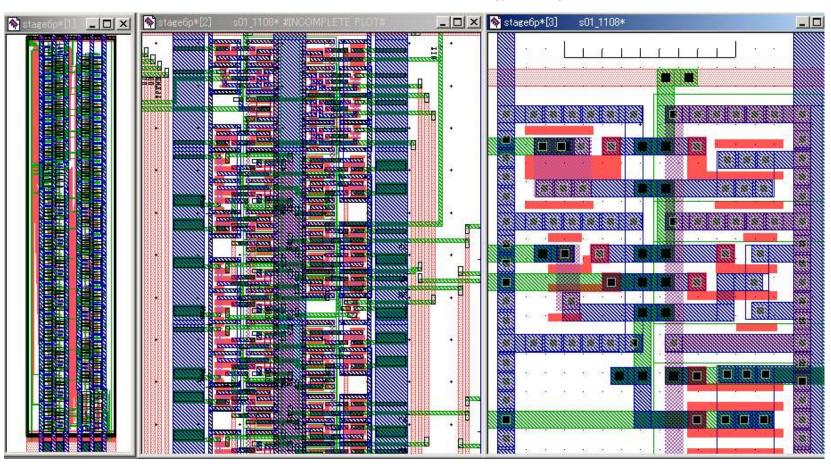

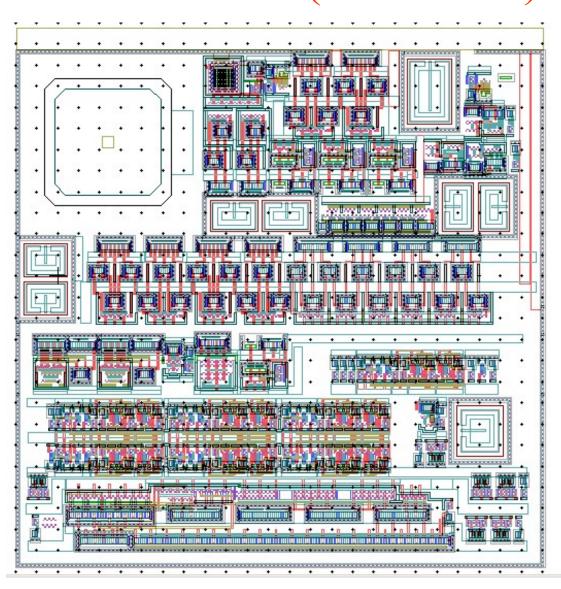

# レイアウト設計

CMOSプロセスに対応する露光マスクを描くこと

レイアウト設計は、外注することが多いので、この時で 仕様書の整備と再確認をすることが必要かつ重要である。

1) レイアウトの具体例を示す(前置増幅器、抵抗回路)

2) DRC

3) LVS

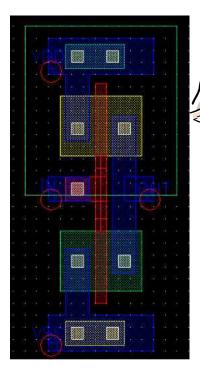

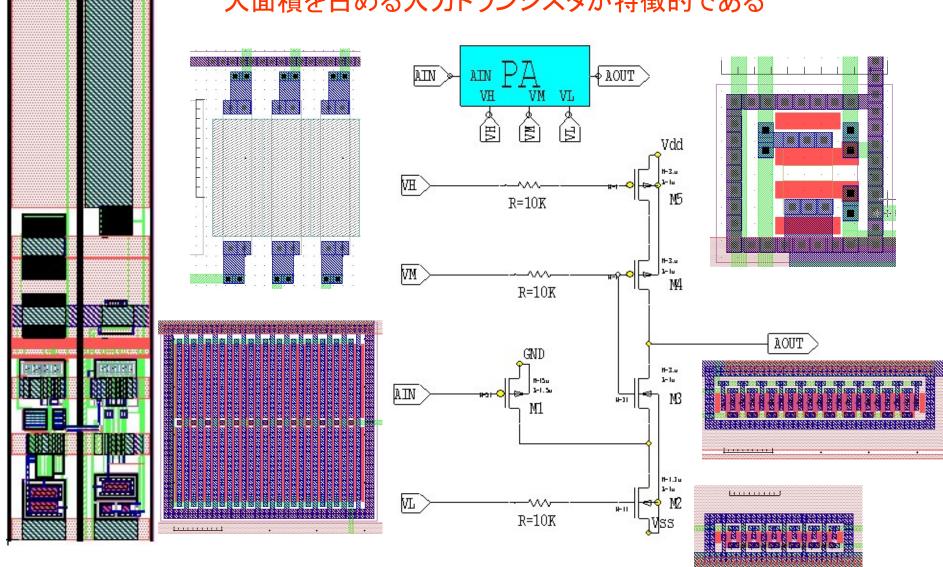

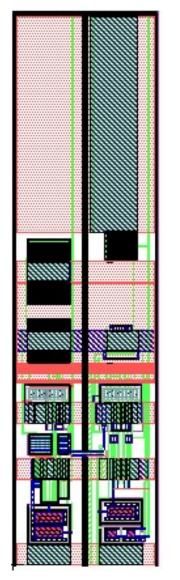

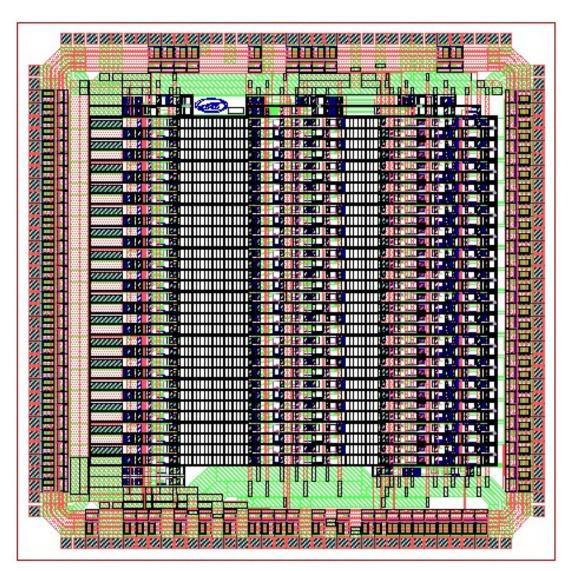

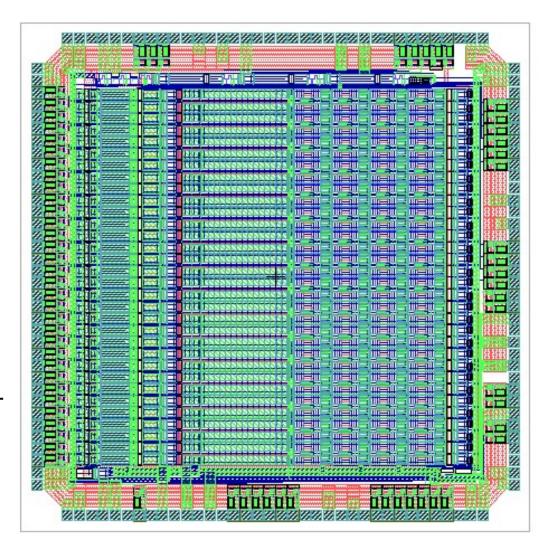

# 前置増幅器のレイアウト

大面積を占める入力トランジスタが特徴的である

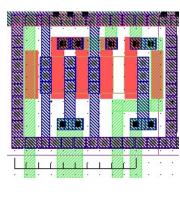

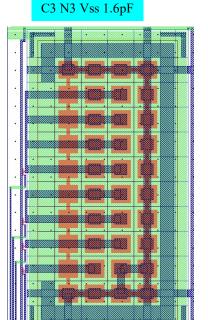

# 抵抗回路のレイアウト

ダミーのポリゲートが吹かされていることに注意

Vss

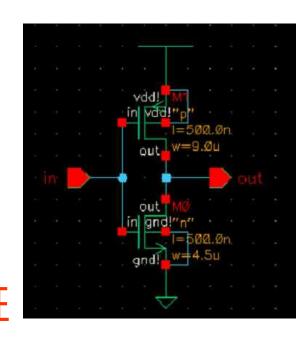

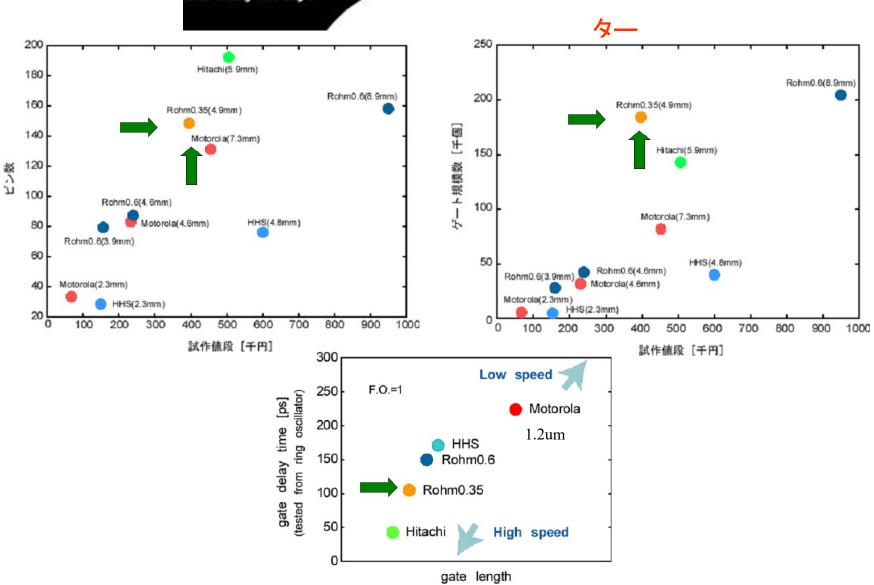

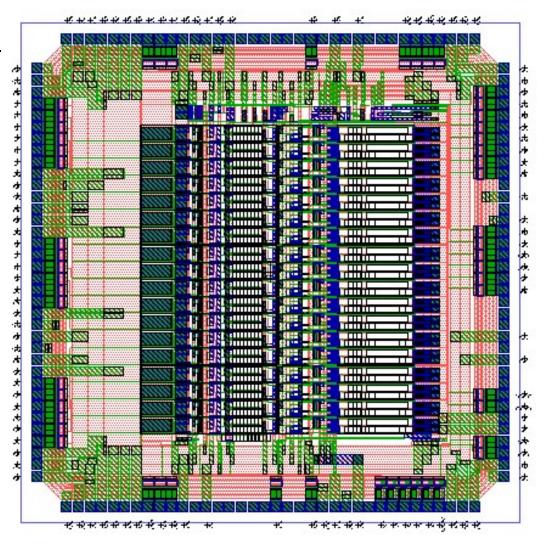

# 論理回路部のレイアウト例

アナログ回路は比較的ゆったりとしていたがディジタル回路では稠密なレイアウトが可能である

### DRC

#### 設計規則に対する設計上の抵触を検出する工程である

#### LVS

#### で記述されたネットリストとレイアウトから抽出されたネットリストと を比較対照する工程である

#### 抽出されたネットリスト

#### SPICEのネットリスト

C0 N1 Vss 0.2pF

C1 N5 Vss 0.4pF

C2 N4 Vss 0.8pF

| C79 VSS 16 | 1.99800E-13 |

|------------|-------------|

| C80 VSS 16 | 1.99800E-13 |

| C81 VSS 16 | 1.99800E-13 |

| C82 VSS 16 | 1.99800E-13 |

| C83 VSS 17 | 1.99800E-13 |

| C84 VSS 17 | 1.99800E-13 |

| C85 VSS 18 | 1.99800E-13 |

| C86 VSS 19 | 1.99800E-13 |

| C87 VSS 16 | 1.99800E-13 |

| C88 VSS 16 | 1.99800E-13 |

| C89 VSS 16 | 1.99800E-13 |

| C90 VSS 16 | 1.99800E-13 |

| C91 VSS 17 | 1.99800E-13 |

| C92 VSS 17 | 1.99800E-13 |

| C93 VSS 18 | 1.99800E-13 |

|            |             |

```

CC1 RLO VM 2.69280E-16

CC2 RLO VDD 3.93420E-15

CC3 RLO AIN 7.99200E-16

CC4 RLO VSS 1.28943E-14

CC5 VM VDD 5.61180E-15

CC6 VM AIN 7.99200E-16

CC7 VM VSS 1.26425E-14

CC8 AIN VDD 4.84440E-15

CC9 AIN VSS 5.41248E-15

CC10 AIN 15 2.46144E-15

CC11 AIN 24 2.87500E-16

CC12 AOUT VDD 1.59840E-15

CC13 AOUT VSS 4.07737E-14

CC14 AOUT C0 2.36160E-16

CC15 AOUT C1 5.71680E-16

CC16 AOUT C2 5.71680E-16

CC17 AOUT C3 5.71680E-16

CC18 AOUT 13 1.20960E-15

CC19 AOUT 15 3.10768E-15

CC20 C0 VDD 6.27600E-16

CC21 C0 VSS 1.65874E-14

CC22 C0 C1 1.52280E-16

CC23 C0 C2 1.52280E-16

CC24 C0 C3 1.52280E-16

CC25 C1 VDD 6.27600E-16

```

```

CC26 C1 VSS 1.94140E-14

CC27 C1 C2 1.52280E-16

CC28 C1 C3 1.52280E-16

CC29 C2 VDD 6.27600E-16

CC30 C2 VSS 2.16160E-14

CC31 C2 C3 1.52280E-16

CC32 C3 VDD 6.27600E-16

CC33 C3 VSS 2.59496E-14

CC34 11 VDD 3.97345E-14

CC35 11 VSS 3.34900E-15

CC36 11 13 9.07200E-16

CC37 11 15 2.41920E-15

CC38 12 VDD 2.01848E-15

CC39 12 VSS 4.18735E-14

CC40 12 13 1.22085E-15

CC41 12 20 1.20960E-15

CC42 12 21 9.07200E-16

CC43 12 29 2.87500E-16

CC44 12 30 2.87500E-16

CC45 13 VDD 7.01411E-15

CC46 13 VSS 2.07688E-14

CC47 13 22 3.02400E-16

CC48 14 VDD 5.71456E-15

CC49 14 22 3.02400E-16

CC50 15 VDD 2.87840E-15

```

```

CC51 15 VSS 7.73580E-15

CC52 15 24 1.21120E-15

CC53 15 25 1.21120E-15

CC54 16 VDD 1.33974E-13

CC55 16 VSS 2.25064E-14

CC56 17 VDD 6.69872E-14

CC57 17 VSS 1.05768E-14

CC58 18 VDD 3.34936E-14

CC59 18 VSS 4.61200E-15

CC60 19 VDD 2.31392E-14

CC61 19 VSS 4.61200E-15

CC62 20 VSS 6.26770E-15

CC63 21 VSS 4.70260E-15

CC64 22 VDD 2.40430E-15

CC65 23 VDD 1.19240E-15

CC66 26 VSS 8.91600E-16

CC67 27 VSS 8.54000E-16

CC68 28 VSS 8.91600E-16

CC69 29 VSS 8.91600E-16

CC70 30 VSS 8.91600E-16

```

対応が完全であればファンダリーにサブミットすることができる

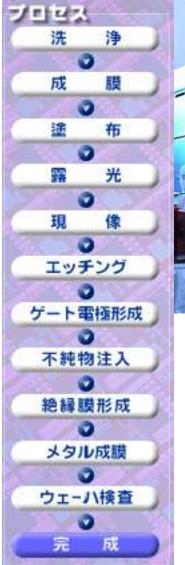

# 半導体プロセスと組立て

VLSI Design & Education Center University of Tokyo

### フロントエンドIPの開発

フロントエンドとは、検出器と直接結合する回路を、IPとは再利用可能な 回路設計上の資産をいう

# 特定の目的で開発した集積回路

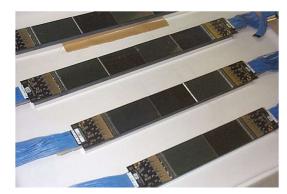

- 1) CdTe-X検出器用多チャン ネル信号処理回路

- 2)3Dピクセル(S.Parker)検出 器用時間・波高同時計測回 路

- 3) HPDアレー検出器用ディジタル読出し回路

#### から汎用性のある回路をIP 化し、

- 1)增幅要素

- 2)バイアス回路

- 3)論理回路

- 4)入出力パッド

これによって軽減された設計負担を新たなIPの開発に振向け、併せてIPの公開を奨めることによりIPの普及と完成度の向上に資する(ことを目的とする。)

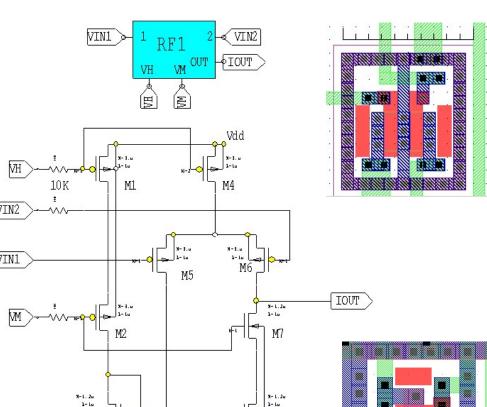

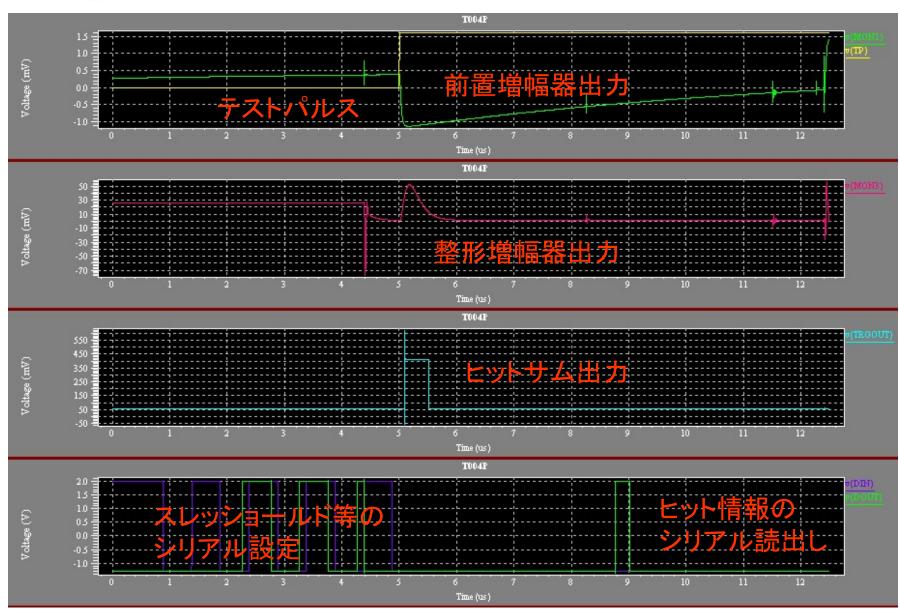

# 事例1

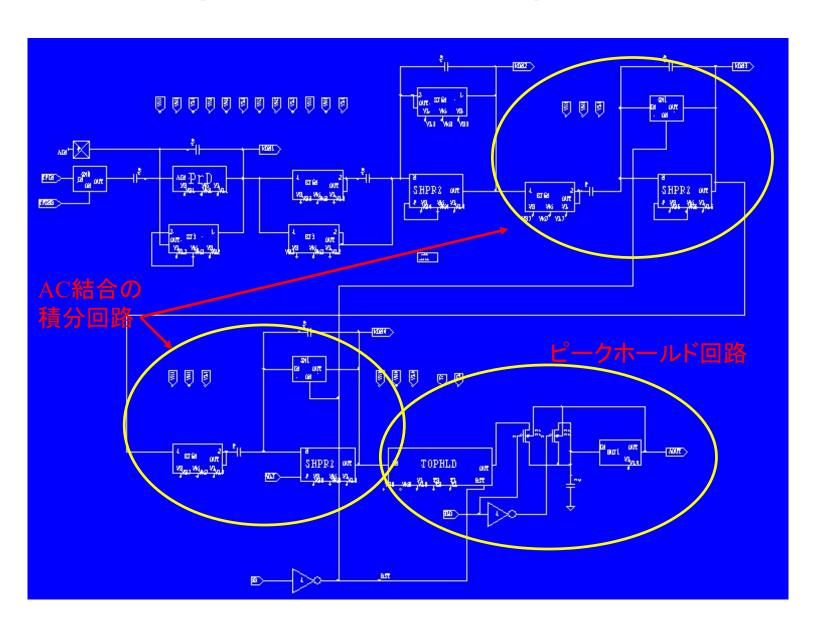

# CAST

#### CdTe-X検出器用多チャンネル信号処理回路(6937Tr's)

16チャンネルからなる低雑音信号処理回路であって、

抵抗回路、

前置增幅器、

ポール・ゼロ補償回路、

整形增幅器、

ヒステリシスコンパレータ、

ピークホールド回路、

低電圧ヒットサム出力回路、

低電圧論理信号I/F

を備え、かつチャンネルごとの ヒット及び波高値を並列に出力 することを特徴とする集積回路。

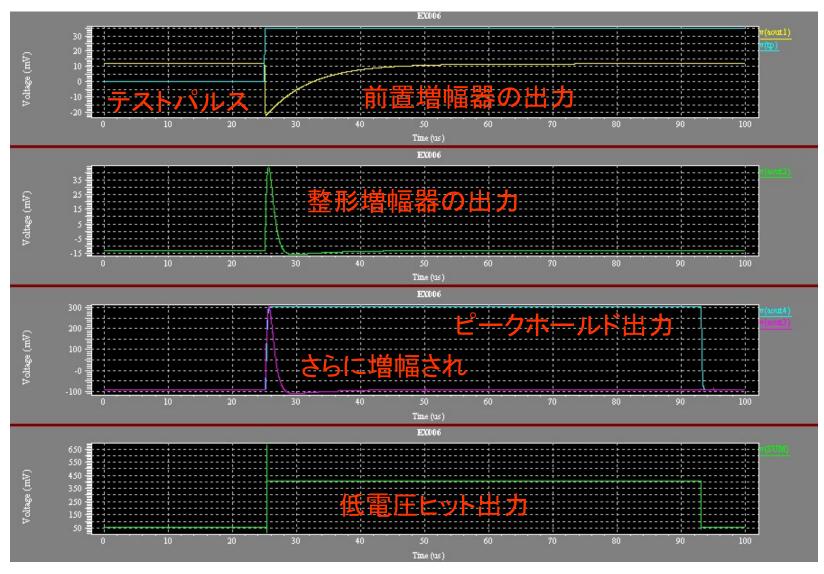

# 事例1の信号波形

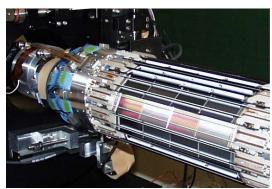

# 事例2

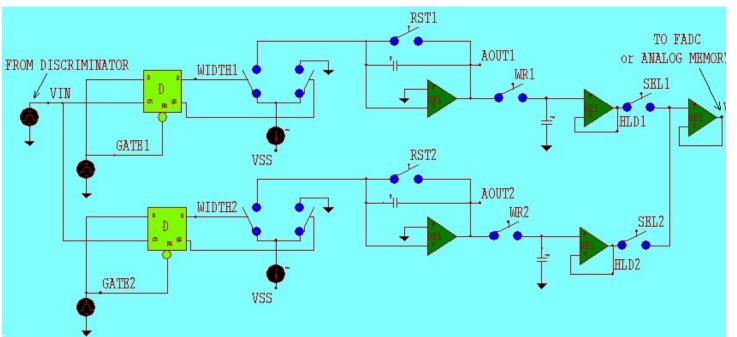

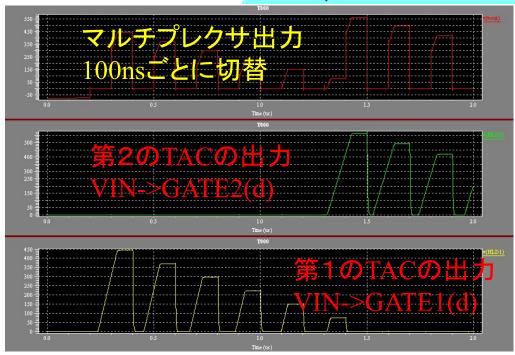

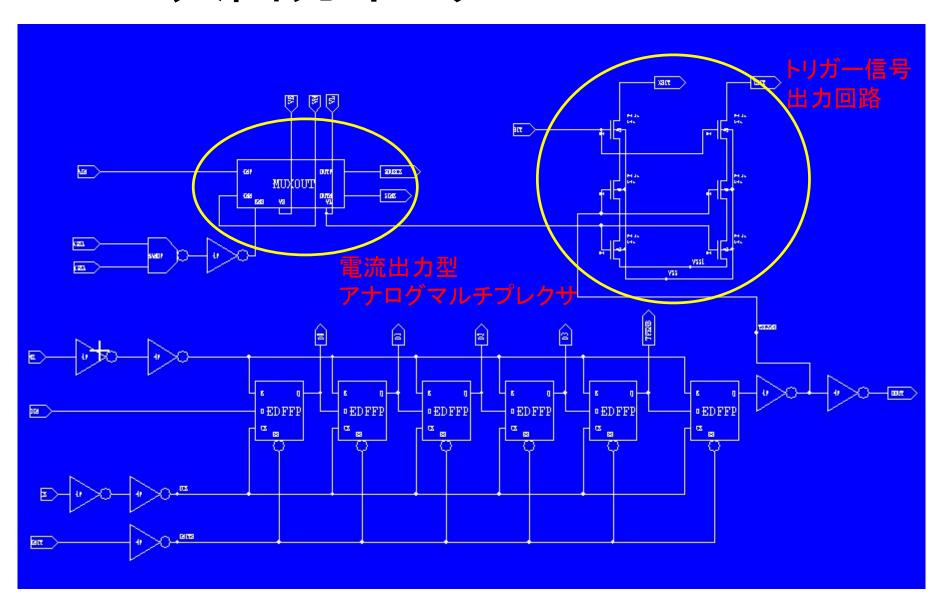

3Dピクセル検出器用時間・波高同時計測回路(12926Tr's)

32チャンネルからなる低雑音信号処理回路であって、

漏れ電流補償機能を有する

抵抗回路

前置增幅器

ローパスフィルター

4重アナログサンプリング回路

ヒステリシスコンパレータ回路

電流型アナログマルチプレクサ

低電圧論理信号I/F

を備え、都合128のアナログ信号と、32のヒット情報をそれぞれ直列に読出すことを特徴とする集積回路

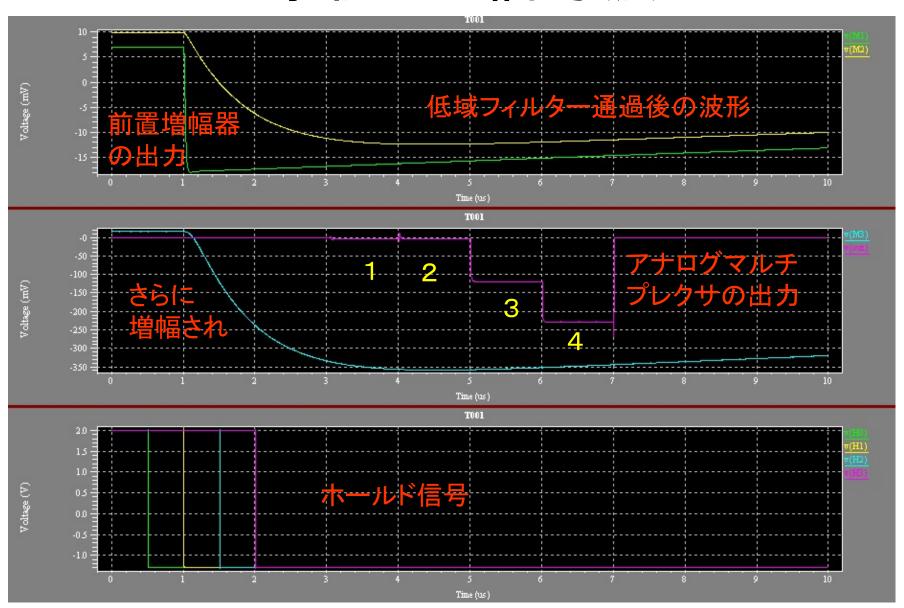

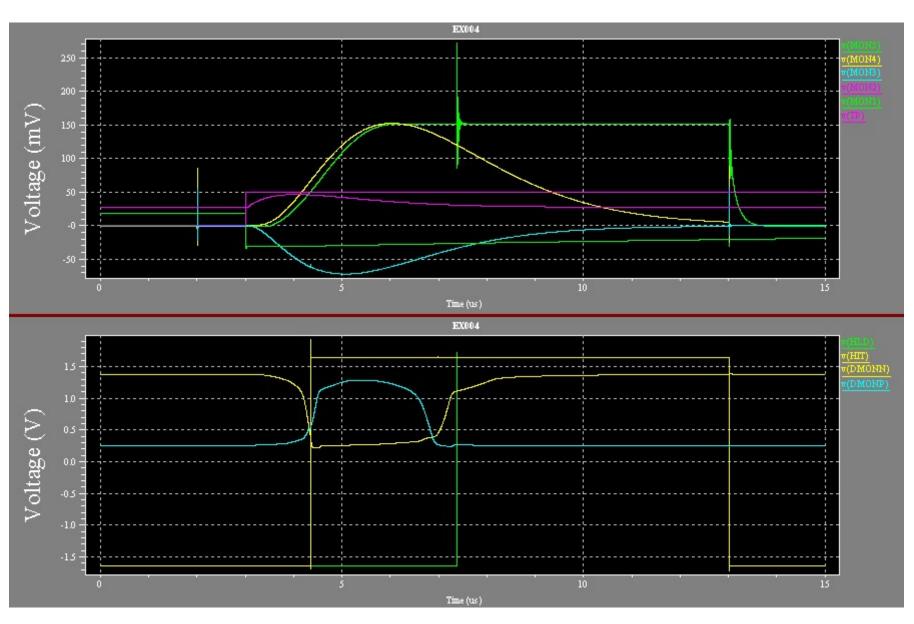

# 事例2の信号波形

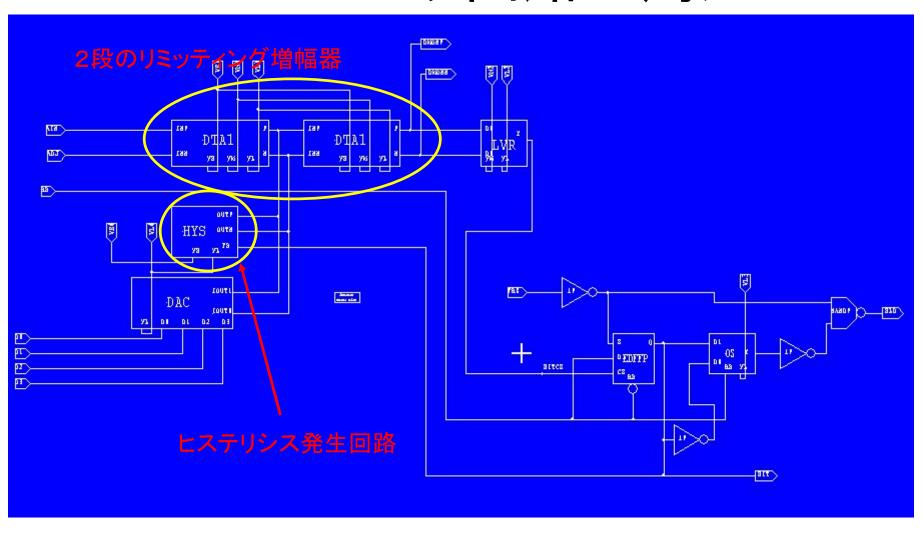

# 事例3

#### HPDアレー検出器用ディジタル読出し回路(24905Tr's)

18チャンネルからなる低雑音信号 処理系であって

抵抗回路、

前置增幅器、

ポール・ゼロ補償付整形増幅器、

ヒステリシスコンパレータ、

閾値微調整用DAC、

ピークホールド回路、

低電圧ヒットサム出力回路、

低電圧論理信号I/F

を備え、かつディジタルパイプライン読出しを特徴とする集積回路

# 事例3の信号波形

## 今後の開発対象として

以下のような回路もスコープの範囲内である

超低雑音回路(CCD) 内蔵A-to-Dコンバータ 積分回路 入力保護回路

高速TOF回路(MAPMT) 高速コンパレータ T-to-Aコンバータ アナログメモリ 2次元増幅器アレー(PIXEL) 低電力化 微調機能(DAC) アナログマルチプレクサ レイアウト・実装等との整合

|                | ALICE        | CMS           | ATLAS          |

|----------------|--------------|---------------|----------------|

| Pixel size     | 50 x 400um   | 150 x 150um   | 50 x 300um     |

| Row*Column     | 256*32=8,192 | 52*53=2,756   | 160*18=2,880   |

| Active area    | 12.8*12.8mm  | 7.8*7.95mm    | 8*5.4mm        |

| Signal readout | Binary       | Analog        | Digital(ToT)   |

| Read latency   | 25.6us       | ~lus          | ~lus           |

| Clk            | 10MHz        | 40MHz         | 40MHz          |

| Тр             | 25ns         | 50ns          | 25ns           |

| FIFO depth FE  | 2(L1)/4(L2)  | 8(time stamp) | 16(time stamp) |

#### TAC

1)サブミクロンCMOS (0.35um)よる

D-FF、電流スイッチ、積分回路、

ホールド回路、アナログマルチプレ

クサを備えた集積回路である。

2)オーバーラップしたゲート(GATE1,

GATE2)を用いた二重系によりデッド

タイムを回避することができる。

# 展望(まとめ)

サブミクロンCMOSを用いたアナログ集積回路を積極的に活用しよう

少し難しい回路への挑戦 超低雑音回路(CCD) 高速TOF回路(MAPMT) 2次元増幅器アレー(PIXEL)

IPの開発と蓄積

高度な集積回路に対する需要の喚起

IPの利用による、迅速、経済、かつ完成度の高い集積回路の設計手段の提供

# Appendix ピクセル化の試み (H15.05.18)

- 1)  $260\mu m$  by  $260\mu m$

- 2) 前置増幅器

- 3) 整形增幅器

CR-RC<sup>3</sup>

- 4) ピークホールド回路

- 5) コンパレータ

- 6) 電流マルチプレクサ

- 7) トリムDAC

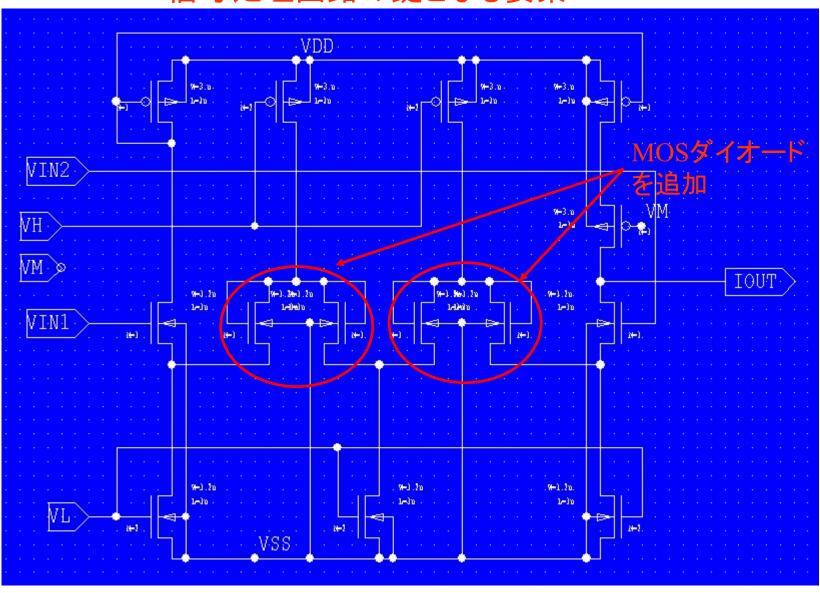

# 改良された抵抗回路

信号処理回路の鍵となる要素

# 前置增幅器、整形增幅器

# コンパレータ回路の周辺

# 入出カインターフェース

# 各部の信号波形

# 以上

# レポート提出要領の確認

- 1)単位の認定を要する者

- 2) 演習問題パート2の内から3問以上を解答すること

- 3)8月25日を一応の期限とする。

- 8月31日までは追完が可能

- 4)電子メールでお送り下さい。

ikeda@post.kek.jp

5)郵送の場合:

郵便番号 305-0801

茨城県つくば市大穂1-1

高エネルギー加速器研究機構

素粒子原子核研究所

池田 博一